Embedded NVM (eNVM) Controllers

UG0331 User Guide Revision 15.0 159

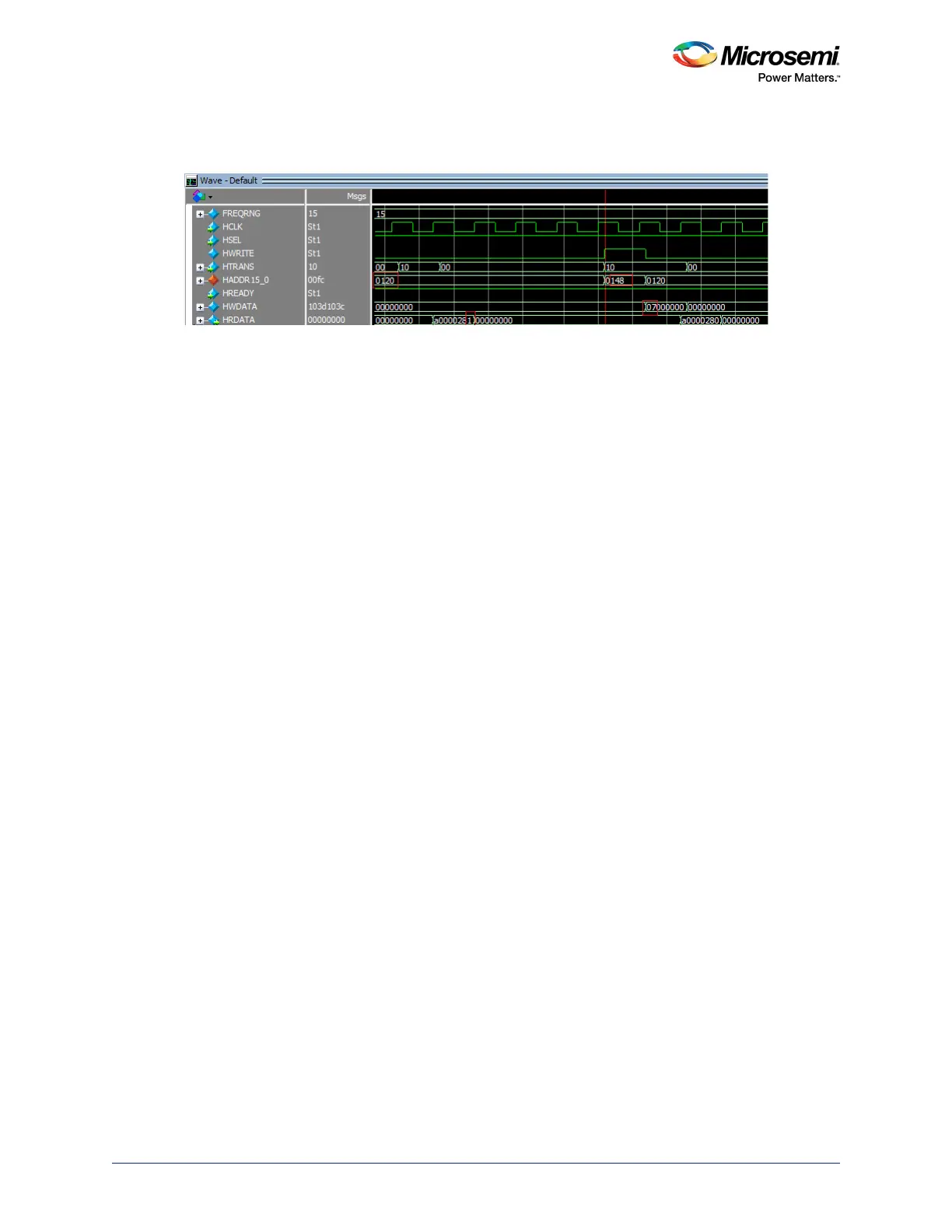

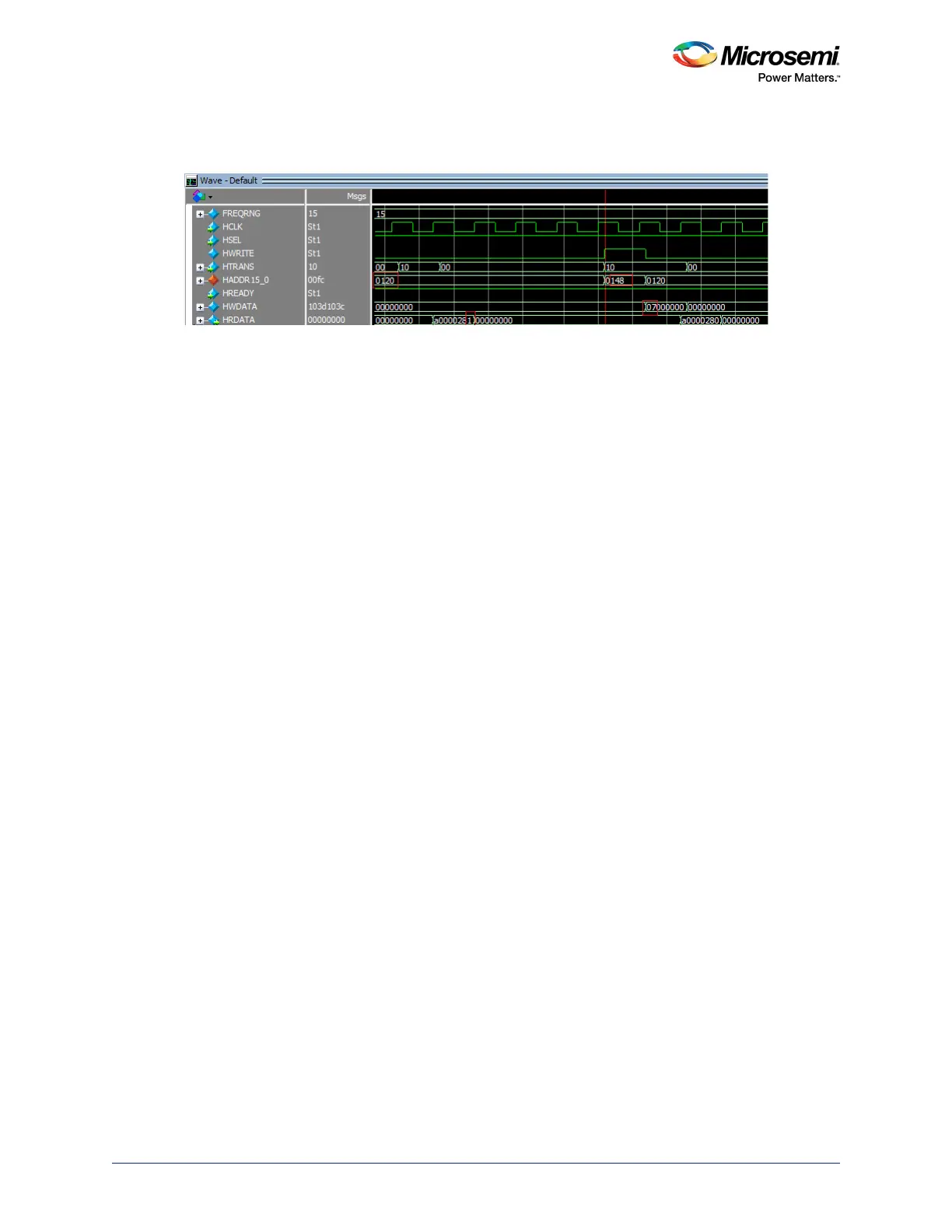

The following figure shows the completion of the ProgramDA command and the issuance of the

ProgramStart command.

Figure 81 • ProgramStart Command

The completion of the eNVM command is confirmed by monitoring the eNVM status register for eNVM

ready and the next command in sequence is sent. VerifyAD, VerifyDA, and VerifyStart commands are

issued by writing corresponding command value into CMD register.

5.2.6 Error Response

The error response, which is indicated by the HRESP signal, is asserted if any of the following conditions

occur:

• AHBL burst read is terminated early or address sequence is not as expected. This should never

occur within the system during normal operation.

• AHBL write transaction addressed to read-only user data array

• AHBL read or write transaction to a protected memory area. Refer to Security, page 159.

Data on HRDATA with error response is zero. A write transaction addressed to read-only Control register

such as RD or RDT will not trigger an error response. However, the data in these registers will not be

affected.

5.2.7 Interrupt to Cortex-M3 Processor

Setting the Control registers INTEN[10:0], as shown in Table 112, page 180, allows the user to configure

HINT (INTISR[17] and INTISR[18] of Cortex-M3 processor) to assert an interrupt on any active status

events from eNVM, such as the assertion of any status bit from eNVM or when an internal eNVM

operation ends.

After HINT is asserted, the Cortex-M3 processor determines the next steps. The Cortex-M3 processor

can respond to the interrupt and then clear HINT by writing 1 to bit 0 of the write-only register

CLRHINT[2:0] (HADDR = 0x158) in Table 112, page 180. If the Cortex-M3 processor decides to ignore

the interrupt (by masking it out), the interrupt is cleared if read or write continues and the interrupt-

triggering events are not re-occurring. If the same triggering event happens again, HINT will remain

asserted.

5.3 Security

The eNVM is protected using four levels of security features:

• The eNVM page protection uses two levels: factory lock and user lock. Factory lock is not accessible

for the user. Refer to the Set Lock Bit and User Unlock Commands, page 153.

• There are two or four special sectors per eNVM array that can be protected for read and write,

depending on which entity is accessing the region as shown in Figure 82, page 160 through

Figure 86, page 162. On devices with smaller or bigger eNVMs, the upper 4 KB special sector is

aligned to the top 4 KB region of the eNVM. These user-protectable 4 KB special sectors can be

configured by Libero software, see Figure 93, page 172.

• There are two private regions in M2S060, M2S090, and M2S150 as shown in Figure 85, page 161

and Figure 86, page 162 which are reserved for storing device certificate, eNVM digest, security

keys and so on. Only system controller can access the private regions. See eNVM Pages for Special

Purpose Storage, page 163

Loading...

Loading...