Serial Peripheral Interface Controller

UG0331 User Guide Revision 15.0 517

14.2.3.1 Initialization Sequence

1. Select the type of transfer protocol by using the TRANSFPRTL bit of the SPI CONTROL register.

2. Enable SPI by writing 0 to the RESET bit of the CONTROL register.

3. Reset the transmit/receive buffers and the data frame size.

14.2.3.2 SPI Status at Reset

After SPI reset, the slave select (SPI_X_SS[X]) pins are held to the default values of logic High. After

selecting SPI mode and enabling the SPI controller, the SPI_X_SS[x] lines are changed to the default

values for each protocol. Refer to the SPI Control Register (CONTROL), page 528. After reset, the clock

out (SPI_X_CLK) is at logic Low. At reset, the FIFOs are cleared and their respective read and write

pointers are set to zero. Similarly, all the internal registers of the SPI controller are reset to their default

values, as explained in the SPI Register Summary, page 527.

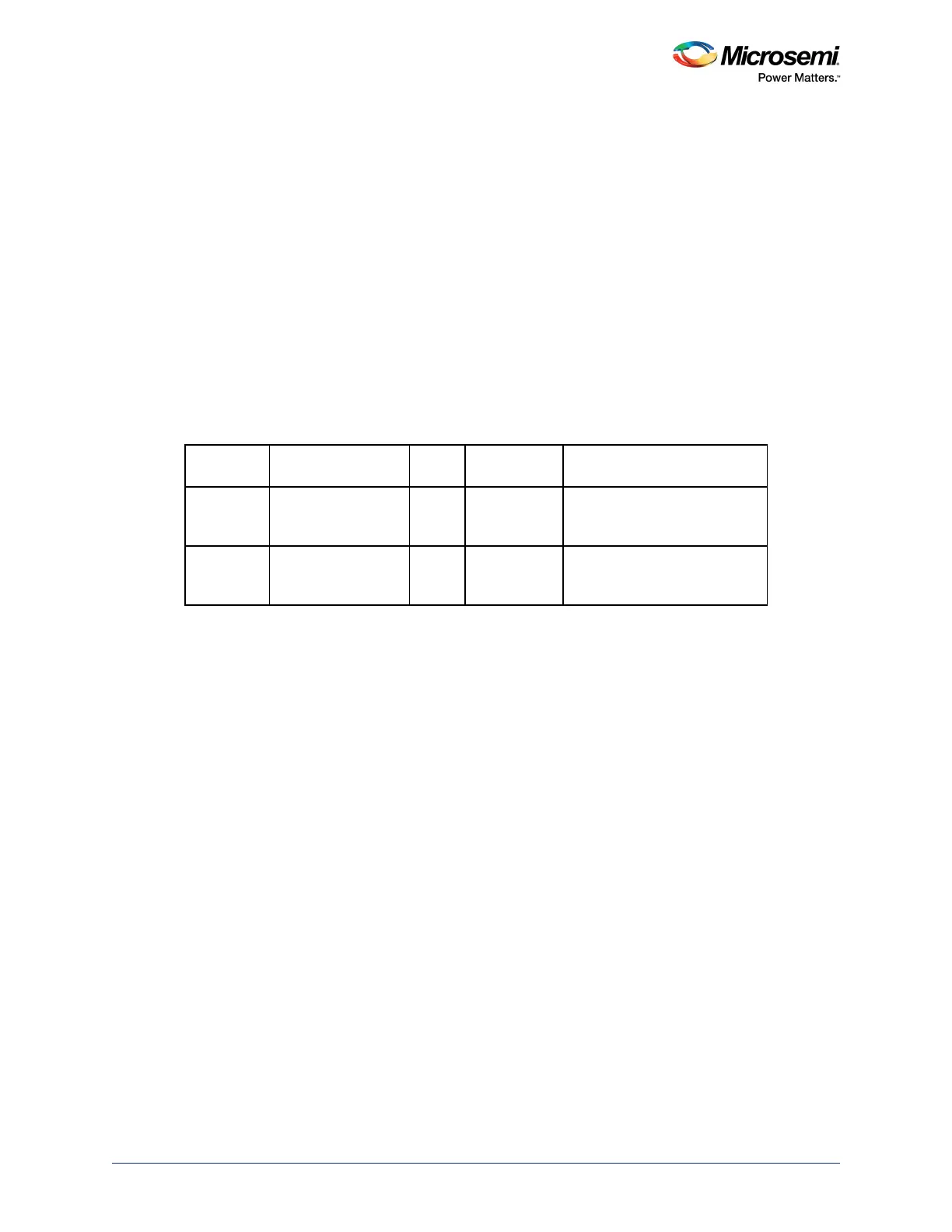

An option is provided to reset the SPI peripherals by writing to bit 9 or bit 10 in the system register,

SOFT_RESET_CR. The soft resets are encoded in the following table. At power-up, the reset signals are

asserted 1. It keeps the SPI peripherals in a reset state. The SPI peripheral becomes active when the bit

is set to 0, as shown in the table.

14.2.3.3 SPI Clock Requirements

The SPI_0 and SPI_1 peripherals are clocked by APB_0_CLK on APB bus 0, and APB_1_CLK on APB

bus 1. These clocks are derived from the main MSS clock, M3_CLK. Each APB clock can be

programmed individually as M3_CLK is divided by 1, 2, 4, or 8. Refer to the UG0449: SmartFusion2 and

IGLOO2 Clocking Resources User Guide for more information.

The SPI clocks in master mode are derived from APB_0_CLK / APB_1_CLK. Master mode and slave

mode SPI data rates depend on the APB clock, as given below.

• Master mode SPI data rate

• Programmable from APB_X_CLK/256 to APB_X_CLK/2

• Programmable from APB_X_CLK /65556 to APB_X_CLK /256 in powers of 2

• Maximum data rate is APB_X_CLK/2

• Slave mode SPI data rate operates up to

• APB_X_CLK for frame sizes (frame size ≥ 8)

• APB_X_CLK /2 for frame sizes (frame size 4 to 7)

14.2.4 Details of Operation

This section describes the SPI controller operation including FIFO, modes of data transfer, interrupts,

and error handling.

14.2.4.1 SPI Transmit and Receive FIFO Flags

The SPI controller contains two, 4×32 (depth x width) FIFOs, as shown in Figure 205 on page 505. One

is for the receive side and the other is for the transmit side. The TXFIFOFUL and TXFIFOEMP bits of the

Status register indicate the full or empty status of the transmit FIFO. The RXFIFOFUL and RXFIFOEMP

bits of the Status register indicate the full or empty status of the receive FIFO. User logic can poll these

bits to obtain the status of the corresponding FIFO.

Table 496 • Soft Reset Bit Definitions for SPI Peripheral

Bit Number Name R/W Reset Value Description

10 SPI1_SOFTRESET R/W 0x1 Controls reset input to SPI_1

0: Release SPI _1 from reset

1: Keep SPI _1 in reset

9 SPI0_SOFTRESET R/W 0x1 Controls reset input to SPI _0

0: Release SPI _0 from reset

1: Keep SPI _0 in reset

Loading...

Loading...