Inter-Integrated Circuit Peripherals

UG0331 User Guide Revision 15.0 538

15 Inter-Integrated Circuit Peripherals

Philips inter-integrated circuit (I2C) is a two wire serial bus interface that provides data transfer between

many devices. SmartFusion2 SoC FPGAs contain two identical I

2

C peripherals in the microcontroller

subsystem (MSS I2C_0 and MSS I2C_1), that provide a mechanism for serial communication between

the SmartFusion2 device and external I

2

C compliant devices.

SmartFusion2 I

2

C peripherals support the following protocols:

•I

2

C protocol as per v2.1 specification

• SMBus protocol as per v2.0 specification

• PMBus protocol as per v1.1 specification

15.1 Features

SmartFusion2 I

2

C peripherals support the following features:

• Master and Slave modes

• 7-bit addressing format and data transfers up to 100 Kbit/s in Standard mode and up to 400 Kbit/s in

Fast mode

• Multi-master collision detection and arbitration

• Own slave address and general call address detection

• Second slave address detection

• System management bus (SMBus) timeout and real-time idle condition counters

• Optional SMBus signals, SMBSUS_N and SMBALERT_N, which are controlled through the APB

interface

• Input glitch or spike filters

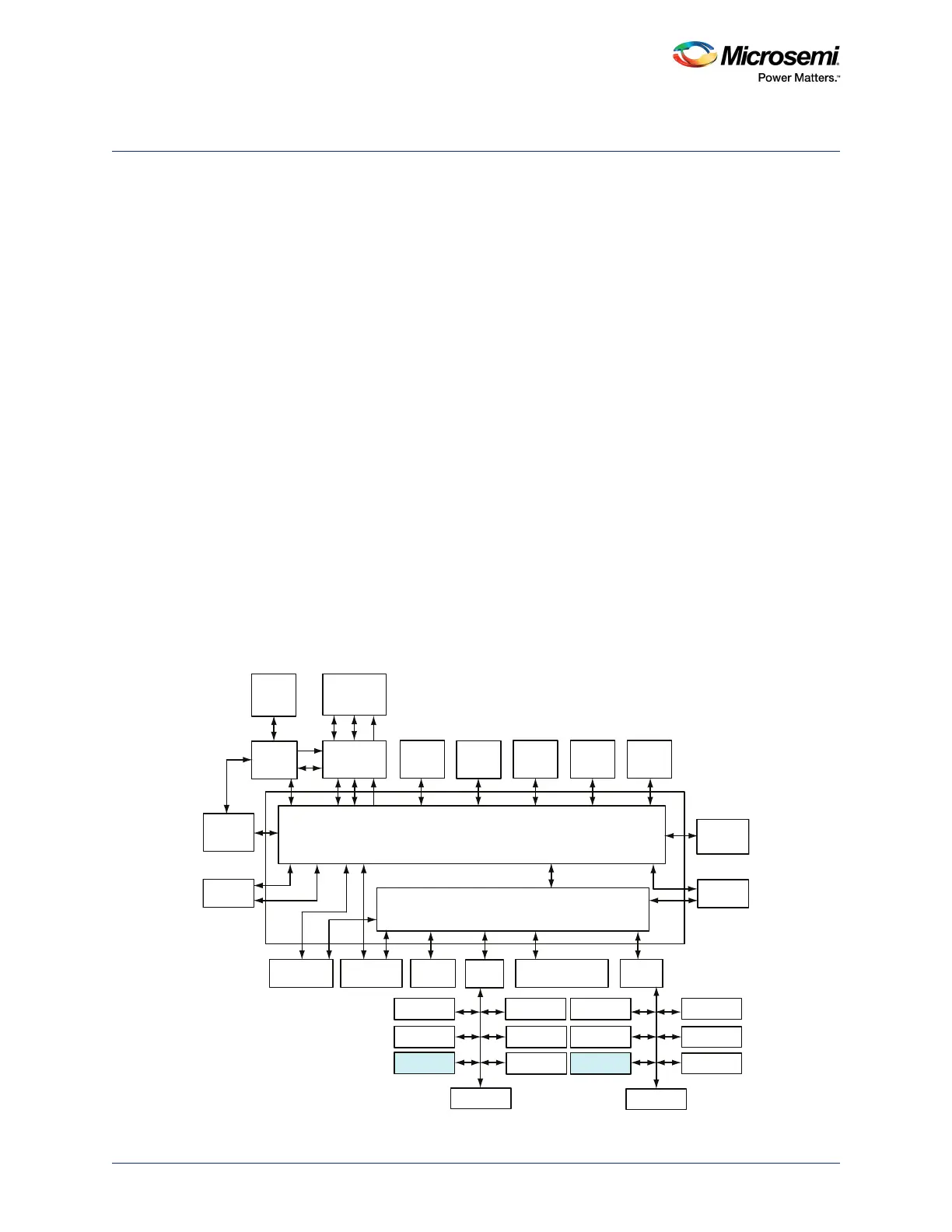

The following figure shows the I

2

C peripherals within the MSS. The I

2

C peripherals are connected to the

advanced high-performance bus (AHB) Matrix through the advanced peripheral bus (APB) interfaces

(APB_0 and APB_1).

Figure 228 • Microcontroller Subsystem Showing I

2

C Peripherals

AHB Bus Matrix

eSRAM_0

System

Controller

Cache

Controller

SD IC

ARM Cortex-M3

Processor

SDI

MSS DDR

Bridge

PDMA

MS6

MM3

AHB To AHB Bridge with Address Decoder

USB OTG

HPDMA

MDDR

APB_0

SYSREG

Triple Speed

Ethernet MAC

FIC_0

MM4 MS4

MS2 MS3 MS0

MS5

MS1

MM5 MM6

MM7

MM8

MM2 MM1 MM0 MM9

IDC

D/S

eNVM_0 eNVM_1 eSRAM_1

FIC_2 (Peripheral

Initialization)

APB_1

MMUART_0

SPI_0

I2C_0

PDMA

Configuration

WATCHDOG

FIIC

TIMERx2

MMUART_1

SPI_1

I2C_1

GPIO

CAN

RTC

COMM_BLK

FIC_1

MSS_FIC

MS6_USB

MS5_MAC MS5_SR MS5_APB0 MS5_FIC2 MS5_APB1

Loading...

Loading...