Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 109

3.7.2.8 System Handler Priority Registers

The SHPR1-SHPR3 registers set the priority level, 0 to 255 of the exception handlers that have

configurable priority.

SHPR1-SHPR3 are byte accessible. See the register summary in Table 50, page 102 for their attributes.

The system fault handlers and the priority field and register for each handler are:

Each PRI_N field is 8 bits wide, but the processor implements only bits [7:M] of each field, and bits [M-

1:0] read as zero and ignore writes.

[7:5] Reserved.

[4] DIV_0_TRP Enables faulting or halting when the processor executes an

SDIV

or

UDIV

instruction with a divisor of 0:

0: do not trap divide by 0

1: trap divide by 0.

When this bit is set to 0, a divide by zero returns a quotient of 0.

[3] UNALIGN_TRP Enables unaligned access traps:

0: do not trap unaligned halfword and word accesses

1: trap unaligned halfword and word accesses.

If this bit is set to 1, an unaligned access generates a UsageFault.

Unaligned

LDM

,

STM

,

LDRD

, and

STRD

instructions always fault irrespective of

whether UNALIGN_TRP is set to 1.

[2] Reserved.

[1] USERSETMPEND Enables unprivileged software access to the STIR, see Software Trigger

Interrupt Register, page 100:

0: disable

1: enable

[0] NONBASETHRDEN

A

Indicates how the processor enters Thread mode:

0: processor can enter Thread mode only when no exception is active.

1: processor can enter Thread mode from any level using the appropriate

EXC_RETURN value, see Exception Return, page 42.

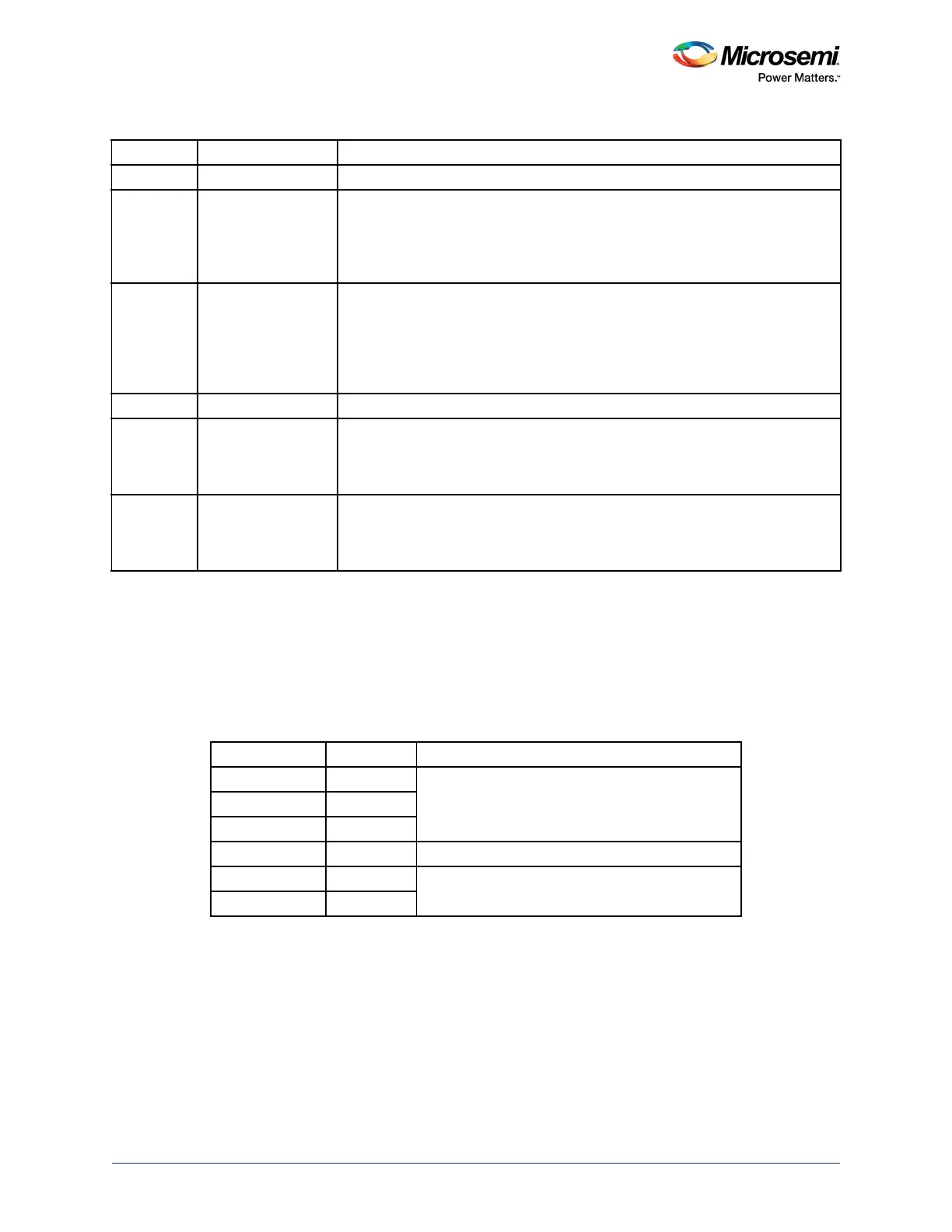

Table 59 • System Fault Handler Priority Fields

Handler Field See

MemManage PRI_4 System Handler Priority Register 2, page 111

BusFault PRI_5

UsageFault PRI_6

SVCall PRI_11 System Handler Priority Register 2, page 111

PendSV PRI_14 System Handler Priority Register 2, page 111

SysTick PRI_15

Table 58 • CCR Bit Assignments (continued)

Bits Name Function

Loading...

Loading...