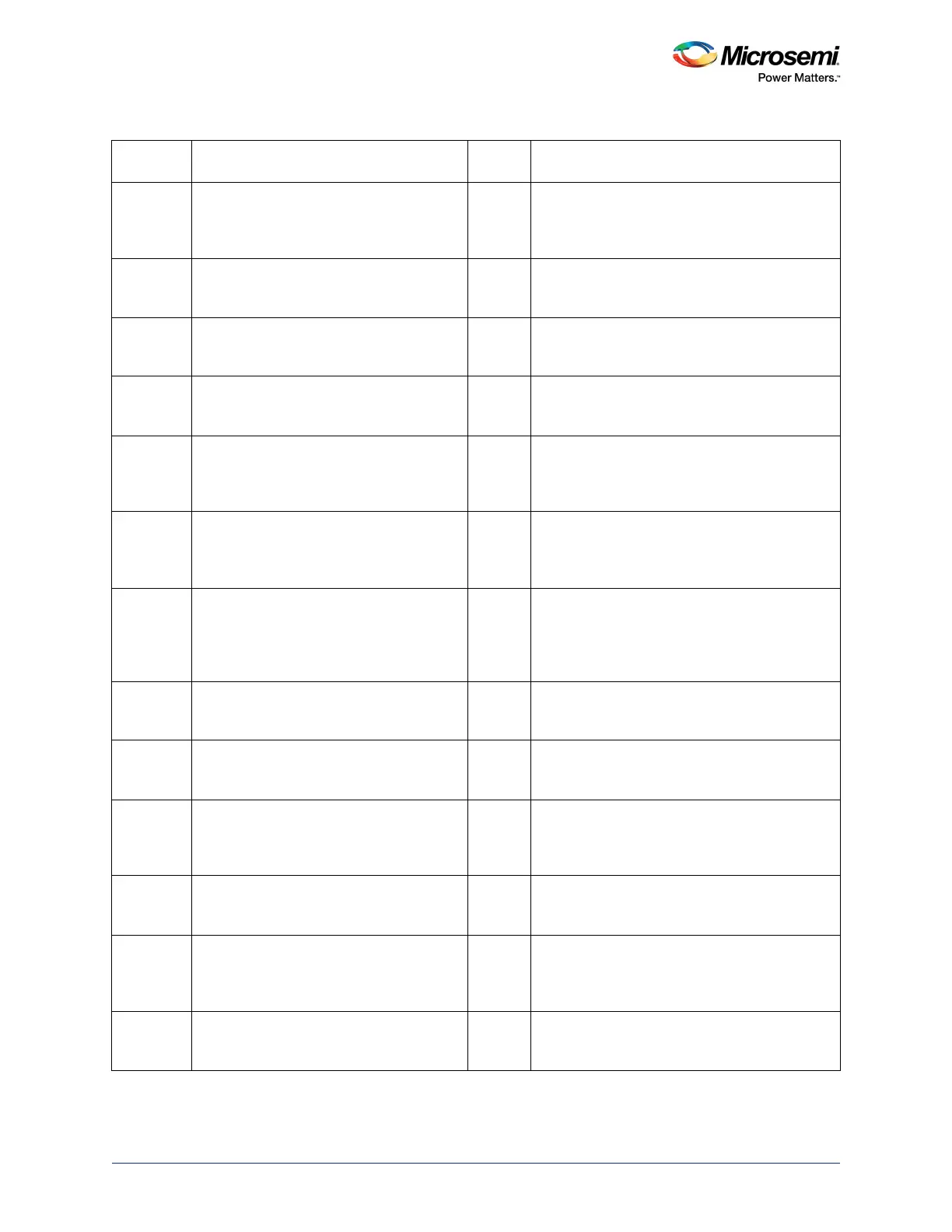

Fabric Interface Interrupt Controller

UG0331 User Guide Revision 15.0 755

9 HPD_XFR_CMP_INT_STATUS 0 Set if the interrupt source for

HPD_XFR_CMP_INT is asserted and the

HPD_XFR_CMP_INT_ENBL interrupt enable bit

in INTERRUPT_ENABLE0 is High.

10 TIMER1_INTR_STATUS 0 Set if the interrupt source for TIMER1_INTR is

asserted and the TIMER1_INTR_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

11 TIMER2_INTR_STATUS 0 Set if the interrupt source for TIMER2_INTR is

asserted and the TIMER2_INTR_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

12 CAN_INTR_STATUS 0 Set if the interrupt source for CAN_INTR is

asserted and the CAN_INTR_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

13 RTC_WAKEUP_INTR_STATUS 0 Set if the interrupt source for

RTC_WAKEUP_INTR is asserted and the

RTC_WAKEUP_INTR_ENBL interrupt enable bit

in INTERRUPT_ENABLE0 is High.

14 WDOGWAKEUPINT_STATUS 0 Set if the interrupt source for

WDOGWAKEUPINT is asserted and the

WDOGWAKEUPINT_ENBL interrupt enable bit

in INTERRUPT_ENABLE0 is High.

15 MSSDDR_PLL_LOCKLOST_INT_STATUS 0 Set if the interrupt source for

MSSDDR_PLL_LOCKLOST_INT is asserted

and the MSSDDR_PLL_LOCKLOST_INT_ENBL

interrupt enable bit in INTERRUPT_ENABLE0 is

High.

16 ENVM_INT0_STATUS 0 Set if the interrupt source for ENVM_INT0 is

asserted and the ENVM_INT0_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

17 ENVM_INT1_STATUS 0 Set if the interrupt source for ENVM_INT1 is

asserted and the ENVM_INT1_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

18 I2C_SMBALERT0_STATUS 0 Set if the interrupt source for I2C_SMBALERT0

is asserted and the I2C_SMBALERT0_ENBL

interrupt enable bit in INTERRUPT_ENABLE0 is

High.

19 I2C_SMBSUS0_STATUS 0 Set if the interrupt source for I2C_SMBSUS0 is

asserted and the I2C_SMBSUS0_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

20 I2C_SMBALERT1_STATUS 0 Set if the interrupt source for I2C_SMBALERT1

is asserted and the I2C_SMBALERT1_ENBL

interrupt enable bit in INTERRUPT_ENABLE0 is

High.

21 I2C_SMBSUS1_STATUS 0 Set if the interrupt source for I2C_SMBSUS1 is

asserted and the I2C_SMBSUS1_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

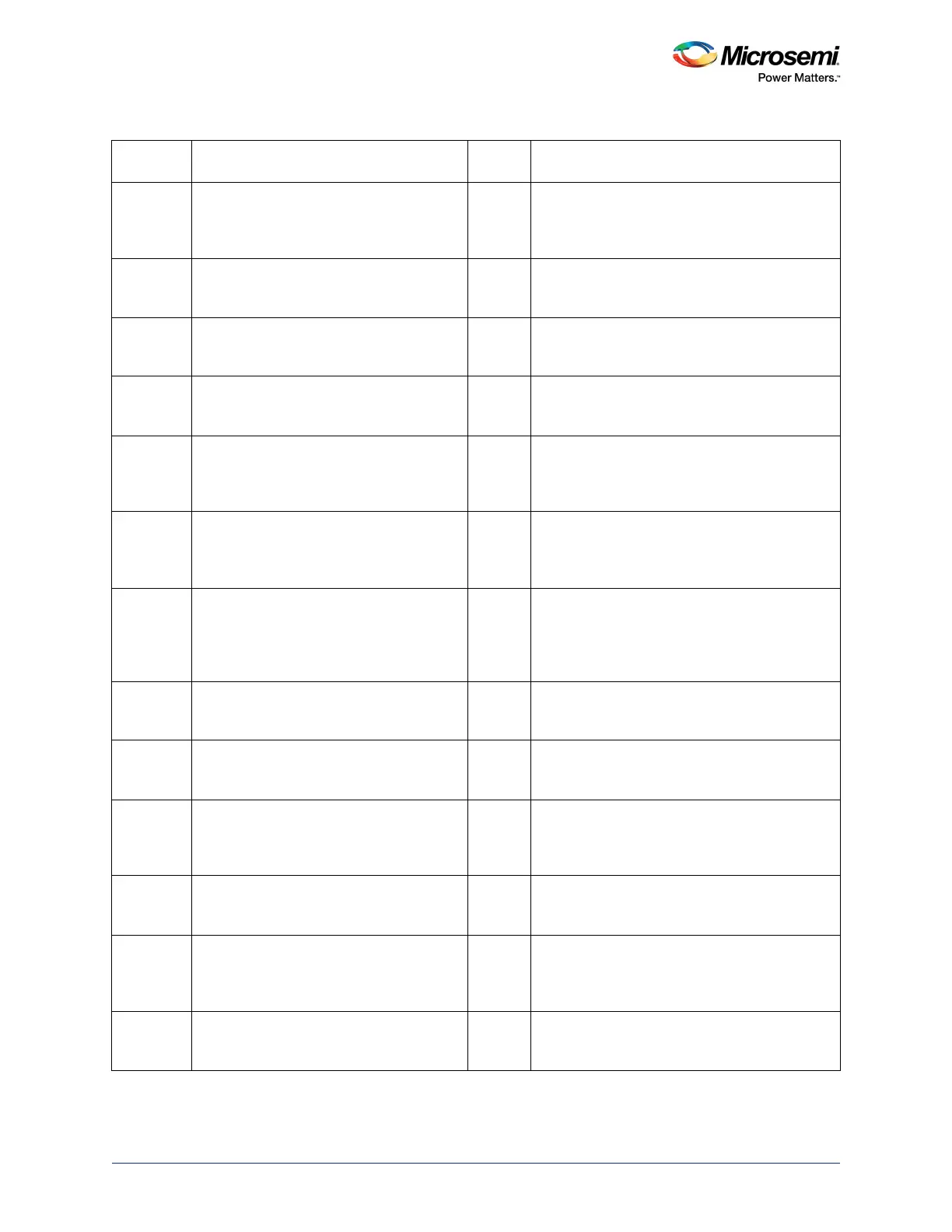

Table 775 • INTERRUPT_REASON0 (continued)

Bit

Number

Name

Reset

Value

Description

Loading...

Loading...