Embedded NVM (eNVM) Controllers

UG0331 User Guide Revision 15.0 147

eNVM Array: The eNVM array is connected to a 25 MHz internal oscillator. This 25 MHz internal

oscillator is used during device start up to initialize the NVM controller. It is also used for eNVM program

operation. For other eNVM operations (Read and Verify), the eNVM controller operates at the M3_CLK.

During eNVM read operations, the NVM controller uses the NV_FREQRNG input to insert wait states to

match with the eNVM array access times. The eNVM array stores the data. Tabl e 94 , page 147 shows

the eNVM memory organization and the total size of the eNVM.

eNVM Controller: Decodes all transactions from the AHBL master and issues the commands to the

eNVM array.

ECC: The error-correcting code (ECC) block in eNVM Controller performs the SECDED. The ECC stores

error correction information with each block to perform SECDED on each 64-bit data word. ECC does not

consume any eNVM array bits. Refer to Table 113, page 184 for ECC status information. ECC block in

eNVM Controller is enabled by default. The user has no access to control the ECC block.

Read Data Buffer: Contains four 64-bit data words. It functions as a small cache by reading NVM data

as four consecutive 64-bit data words. Data read from the eNVM is stored in read data buffer (RDBUFF)

and presented to AHB read data bus (HRDATA) corresponding to HADDR.

If the data is not available, an eNVM read cycle is invoked to retrieve data from the eNVM array. To

support an 8-bit fixed length wrapping burst, four eNVM read cycles are automatically invoked and data

read from the eNVM is stored in RDBUFF. Read data is presented to HRDATA when the data for the

current read address becomes available.

Assembly Buffer (AB): The eNVM is page-based flash memory. Only one page of data (1,024 bits) can

be written at a time. The assembly buffer stores thirty-two 32-bit data words for programming. During

programming, the assembly buffer cannot be updated. If more than one page is to be written, the page

programming function needs to be called as many times as the number of pages.

Write Data Buffer: The write data buffer provides a secondary 32-word data buffer. This can be updated

with the next 32 words to be programmed during eNVM programming.

eNVM to AHB Controller: This block interfaces the eNVM Controller with the AHB-Lite (AHBL) master

as shown in Figure 66, page 146.

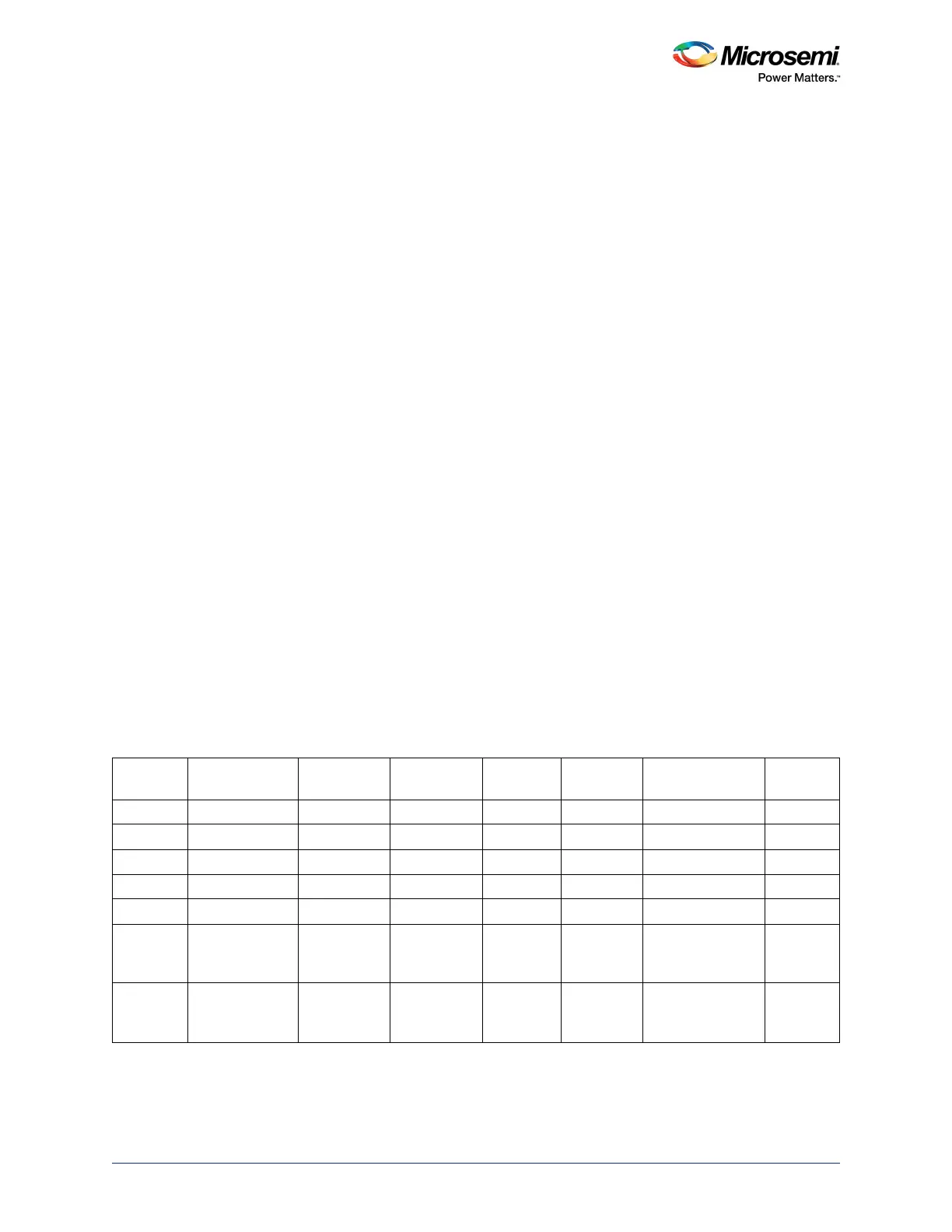

5.2.1 Memory Organization

The eNVM is divided into sectors based on the eNVM size. Each sector is divided into 32 pages. Each

page holds 1,024 bits of data. The following table lists the total available memory and its organization.

Table 94 • Memory Organization

Device NVM Size

Number of

Sectors

Pages per

Sector

Bytes per

Page

Words per

Page

64-Bit Locations

per Page

Total

Bytes

M2S005 128 KB 32 32 128 32 16 131072

M2S010 256 KB 64 32 128 32 16 262, 144

M2S025 256 KB 64 32 128 32 16 262, 144

M2S050 256 KB 64 32 128 32 16 262, 144

M2S060 256 KB 64 32 128 32 16 262, 144

M2S090 512 KB

(two eNVMs,

each 256 KB)

64 per NVM 32 per NVM

per sector

128 32 16 262, 144

per NVM

M2S150 512 KB

(two eNVMs,

each 256 KB)

64 per NVM 32 per NVM

per sector

128 32 16 262, 144

per NVM

Loading...

Loading...