Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 127

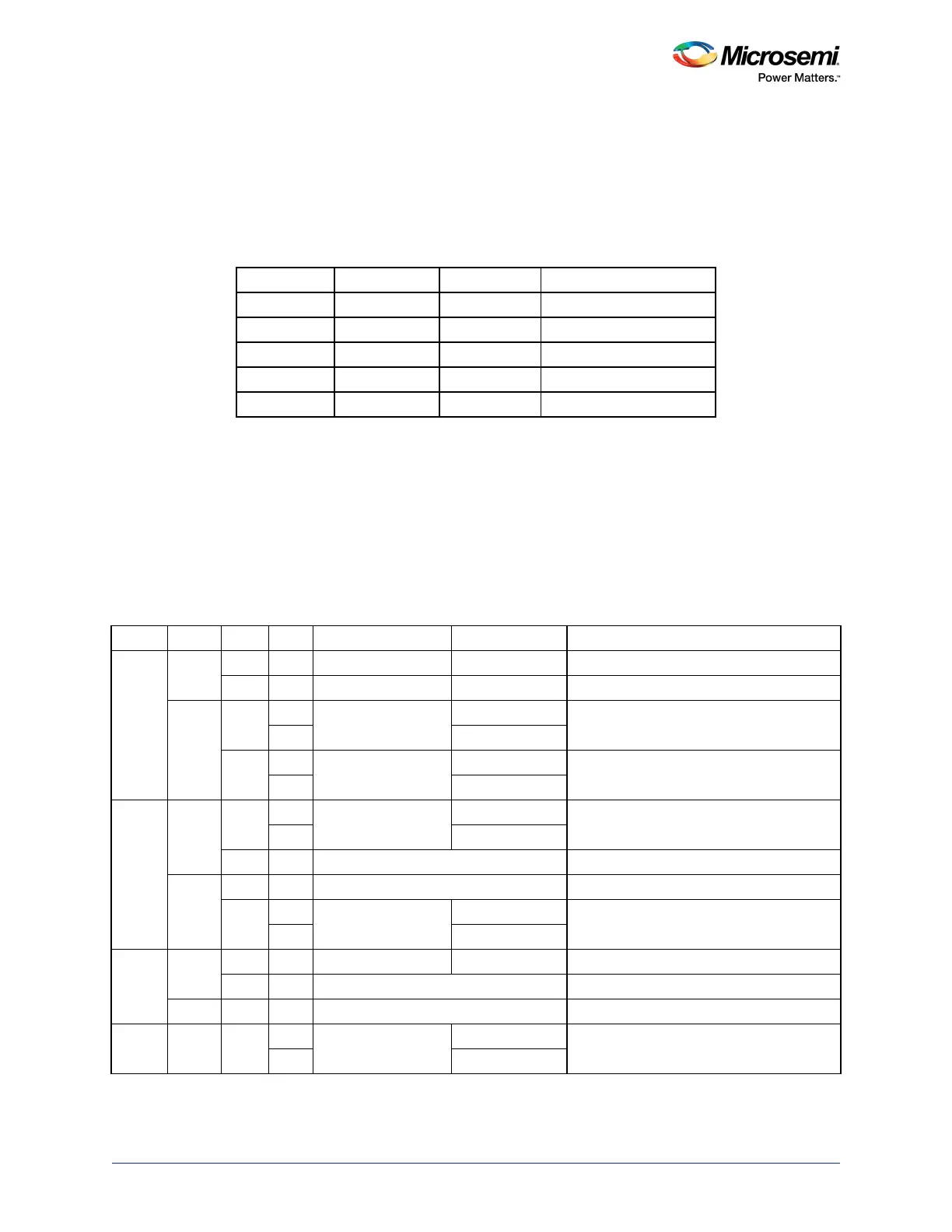

3.7.4.5.1 SIZE Field Values

The SIZE field defines the size of the MPU memory region specified by the MPU_RNR. as follows:

(Region size in bytes) = 2(SIZE+1)

The smallest permitted region size is 32B, corresponding to a SIZE value of 4. The following table

provides example SIZE values, with the corresponding region size and value of N in the MPU_RBAR.

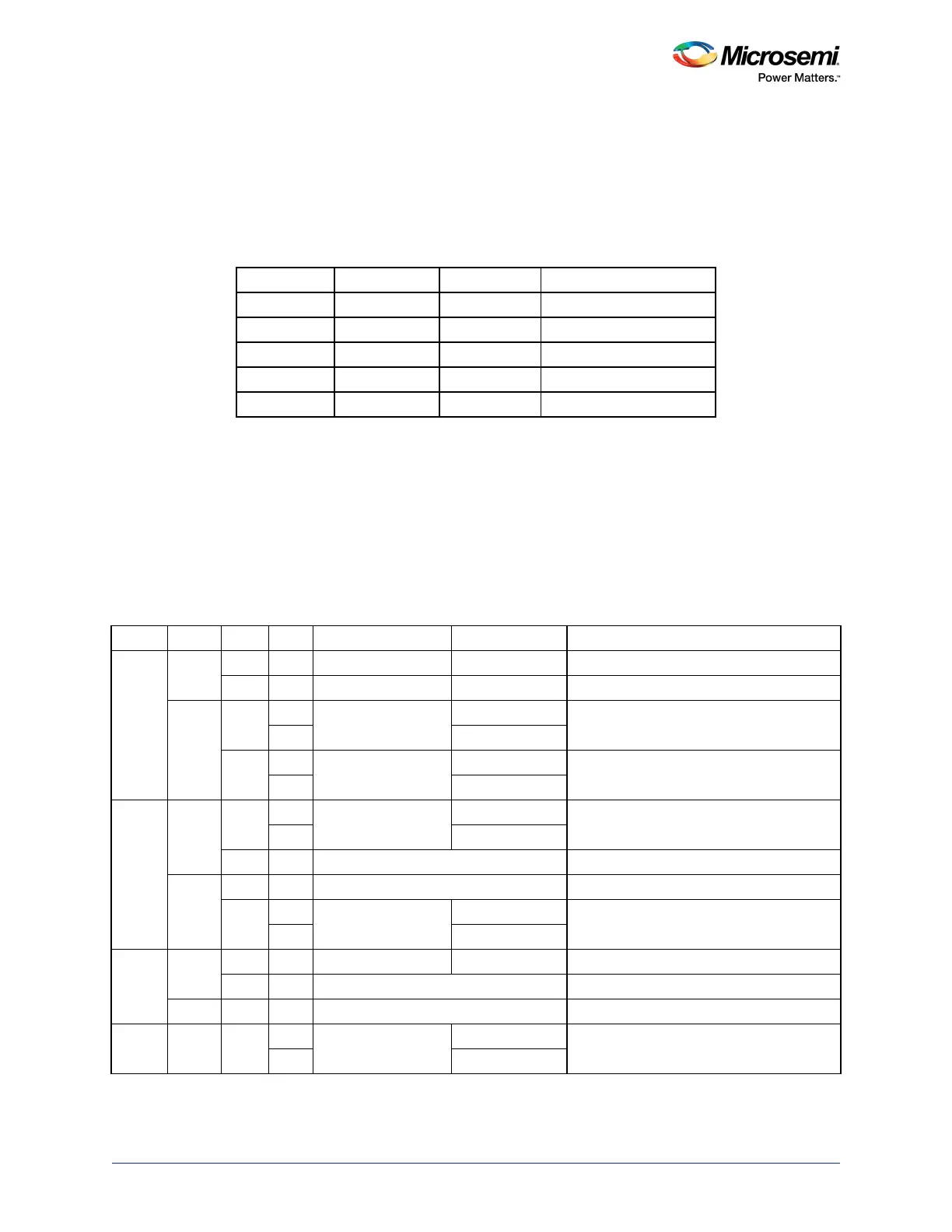

3.7.4.6 MPU Access Permission Attributes

This section describes the MPU access permission attributes. The access permission bits, TEX, C, B, S,

AP, and XN, of the MPU_RASR, control access to the corresponding memory region. If an access is

made to an area of memory without the required permissions, then the MPU generates a permission

fault.

The following table shows the encodings for the TEX, C, B, and S access permission bits.

Table 83 • Example SIZE Field Values

SIZE value Region size Value of N

1

1. In the MPU_RBAR, see MPU Region Base Address Register, page 126.

Note

b00100 (4) 32B 5 Minimum permitted size

b01001 (9) 1KB 10

b10011 (19) 1MB 20

b11101 (29) 1GB 30

b11111 (31) 4GB 32 Maximum possible size

Table 84 • TEX, C, B, and S Encoding

TEX C B S Memory type Shareability Other attributes

b000 0

0 x

1

1. The MPU ignores the value of this bit.

Strongly-ordered Shareable

1 x

a

Device Shareable

1 0 0 Normal Not shareable Outer and inner write-through. No write

allocate.

1 Shareable

1 0 Normal Not shareable Outer and inner write-back. No write

allocate.

1 Shareable

b001 0

0 0 Normal Not shareable Outer and inner non-cacheable.

1 Shareable

1 x

a

Reserved encoding

1 0 x

a

Implementation defined attributes.

1 0 Normal Not shareable Outer and inner write-back. Write and read

allocate.

1 Shareable

b010 0 0 x

a

Device Not shareable Nonshared Device.

1 x

a

Reserved encoding

1x

a

x

a

Reserved encoding

b1BB A A 0 Normal Not shareable Cached memory

2

, BB = outer policy,

AA = inner policy.

2. See Table 85, page 129 for the encoding of the AA and BB bits.

1 Shareable

Loading...

Loading...