Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 367

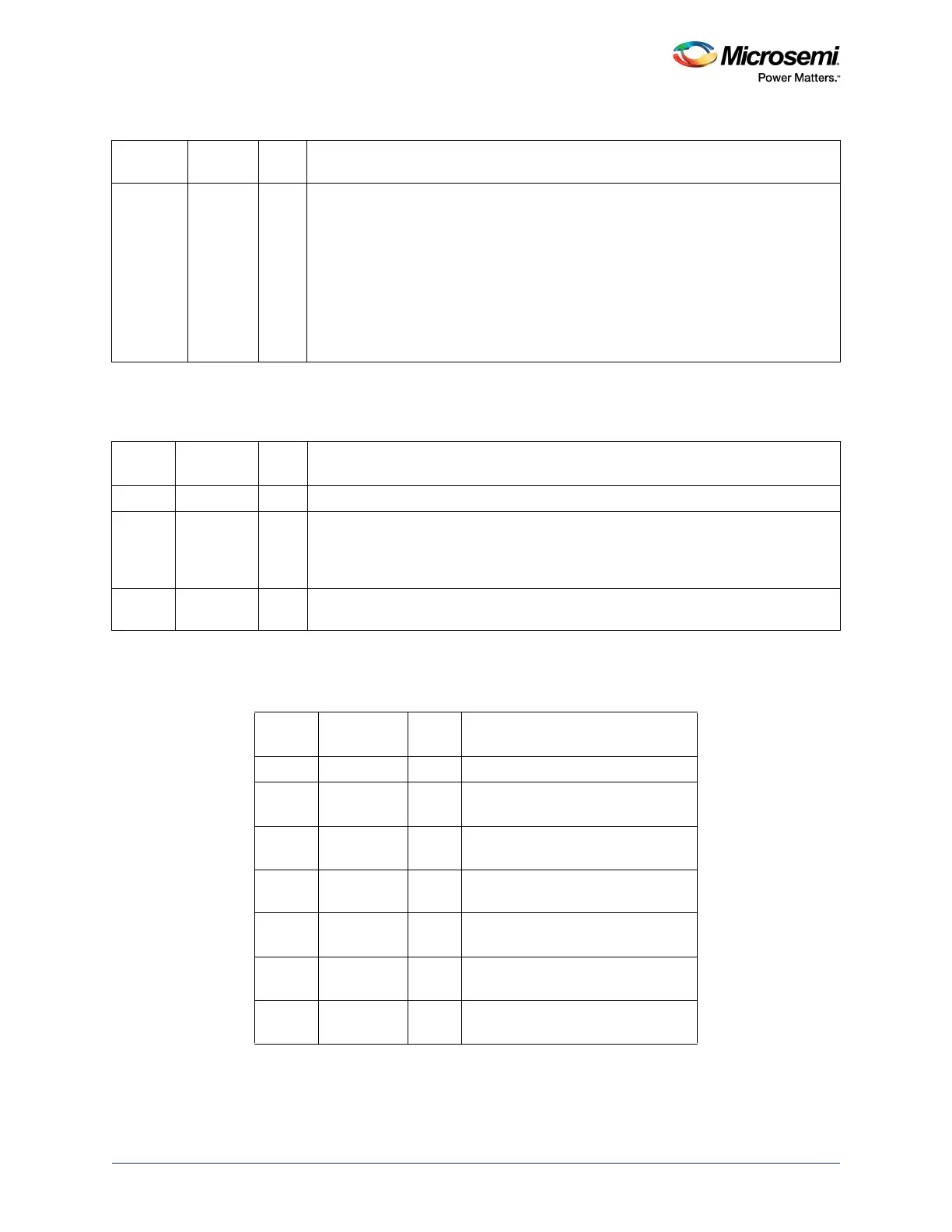

10.3.14.4 LPM_CTRL_REG (Host) Bit Definitions

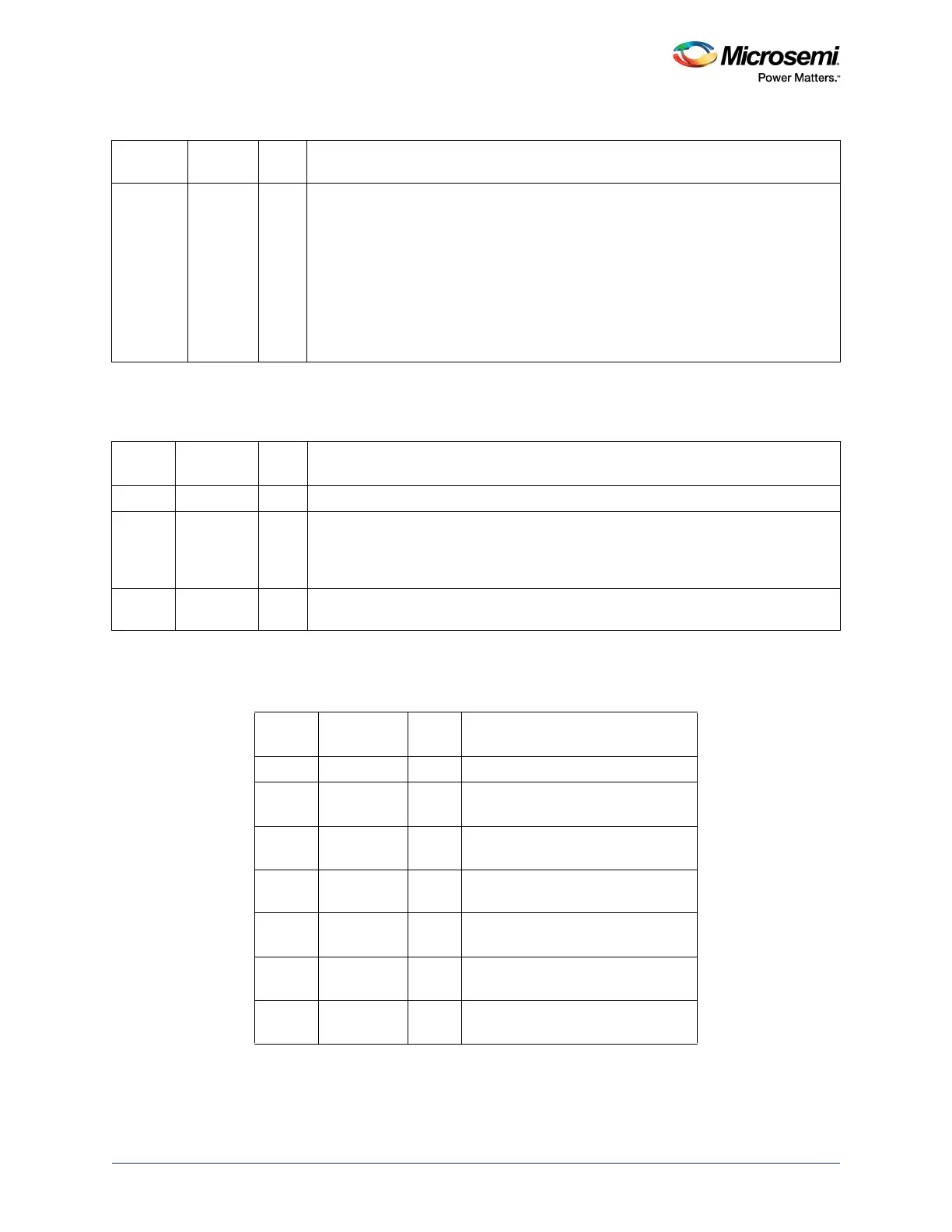

10.3.14.5 LMP_INTR_EN_REG Bit Definitions

0 LPMXMT 0 Instructs the USB controller to transition to the L1 state upon the receipt of the next

LPM transaction. This bit is only effective if LPMEN (bits[3:2] of this register) is set to

11. This bit can be set in the same cycle as LPMEN. If this bit is set to 1 and LPMEN =

11, the USB controller can respond in the following ways:

If any data is not pending (all transmit FIFOs are empty), the USB controller will

respond with an ACK. In this case this bit will self clear and a software interrupt will be

generated.

If any data is pending (data resides in at least one transmit FIFO), the USB controller

will respond with a NYET. In this case, this bit will NOT self clear; however, a software

interrupt will be generated.

Table 307 • LPM_CTRL_REG (0x40043362) (Host)

Bit

Number Name

Reset

Value Function

[7:2] Reserved N/A

1 LPMRES 0 Initiates a RESUME from the L1 state. This bit differs from the classic RESUME bit

(POWER_REG.bit2) in that the RESUME signal timing is controlled by hardware.

When software writes this bit, resume signaling is asserted for a time specified by the

HIRD field (LPM_ATTR_REG.bit[7:4]). This bit is self clearing.

0 LPMXMT 0 Transmits an LPM transaction. This bit is self clearing. This bit will be immediately

cleared upon receipt of any token or three timeouts have occurred.

Table 308 • LPM_INTR_EN_REG (0x40043363)

Bit

Number Name

Reset

Value Function

[7:6] Reserved N/A

5 LPMERREN 0 0: Disable the LPMERR interrupt

1: Enable the LPMERR interrupt

4 LPMRESEN 0 0: Disable the LPMRES interrupt

1: Enable the LPMRES interrupt

3 LPMNCEN 0 0: Disable the LPMNC interrupt

1: Enable the LPMNC interrupt

2 LPMACKEN 0 0: Disable the LPMACK interrupt

1: Enable the LPMACK interrupt

1 LPMNYEN 0 0: Disable the LPMNY interrupt

1: Enable the LPMNY interrupt

0 LPMSTEN 0 0: Disable the LPMST interrupt

1: Enable the LPMST interrupt

Table 306 • LPM_CTRL_REG (0x40043362)(Peripheral) (continued)

Bit

Number Name

Reset

Value Function

Loading...

Loading...