Embedded SRAM (eSRAM) Controllers

UG0331 User Guide Revision 15.0 202

Note: Refer to Figure 101, page 210 for more information on AHB Bus Matrix masters and slaves.

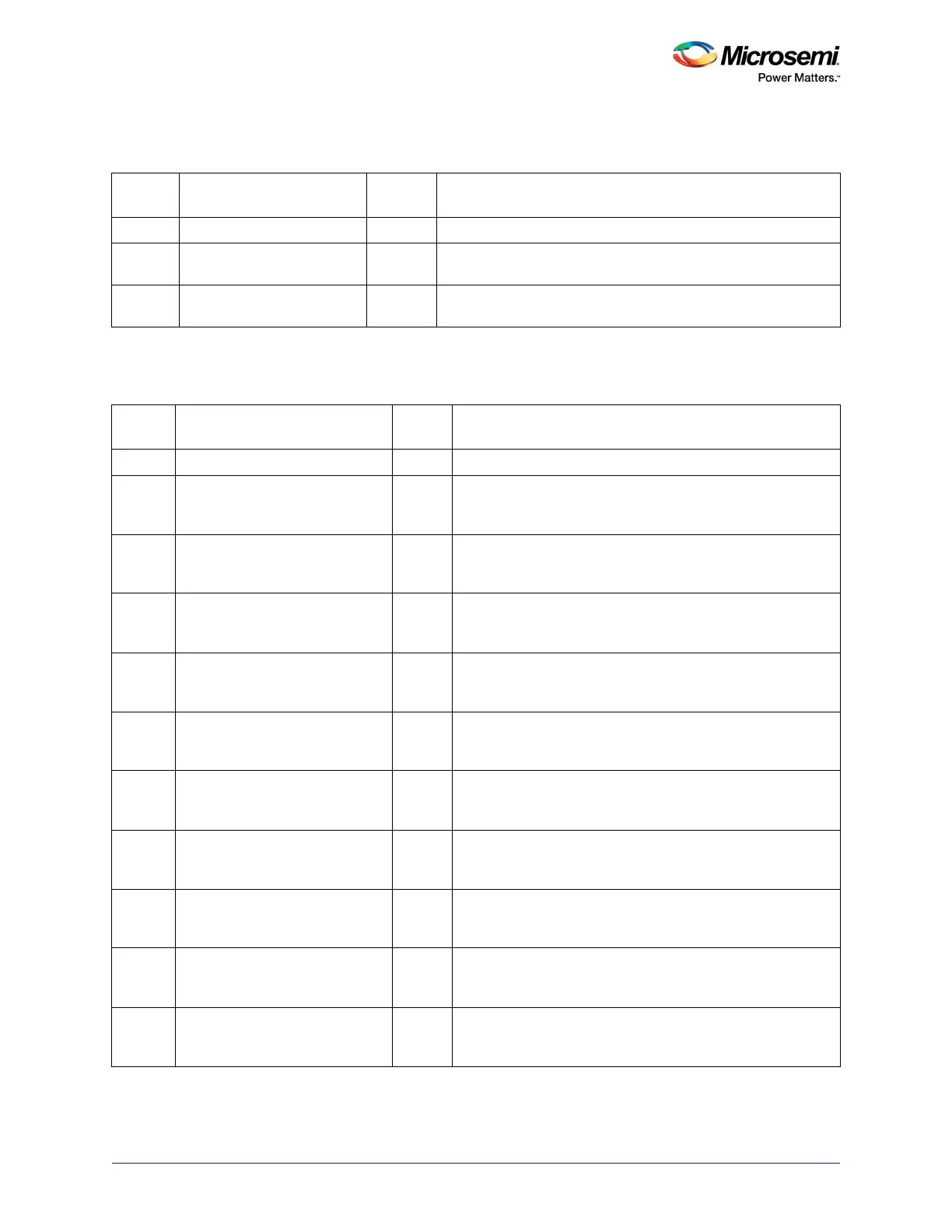

Table 130 • ESRAM1_EDAC_ADR

Bit

Number Name

Reset

Value Description

[31:25] Reserved 0 Reserved

[25:13] ESRAM1_EDAC_2E_AD 0 Stores the address from eSRAM1 on which a 2-bit SECDED

error has occurred.

[12:0] ESRAM1_EDAC_1E_AD 0 Stores the address from eSRAM1 on which a 1-bit SECDED

error has occurred.

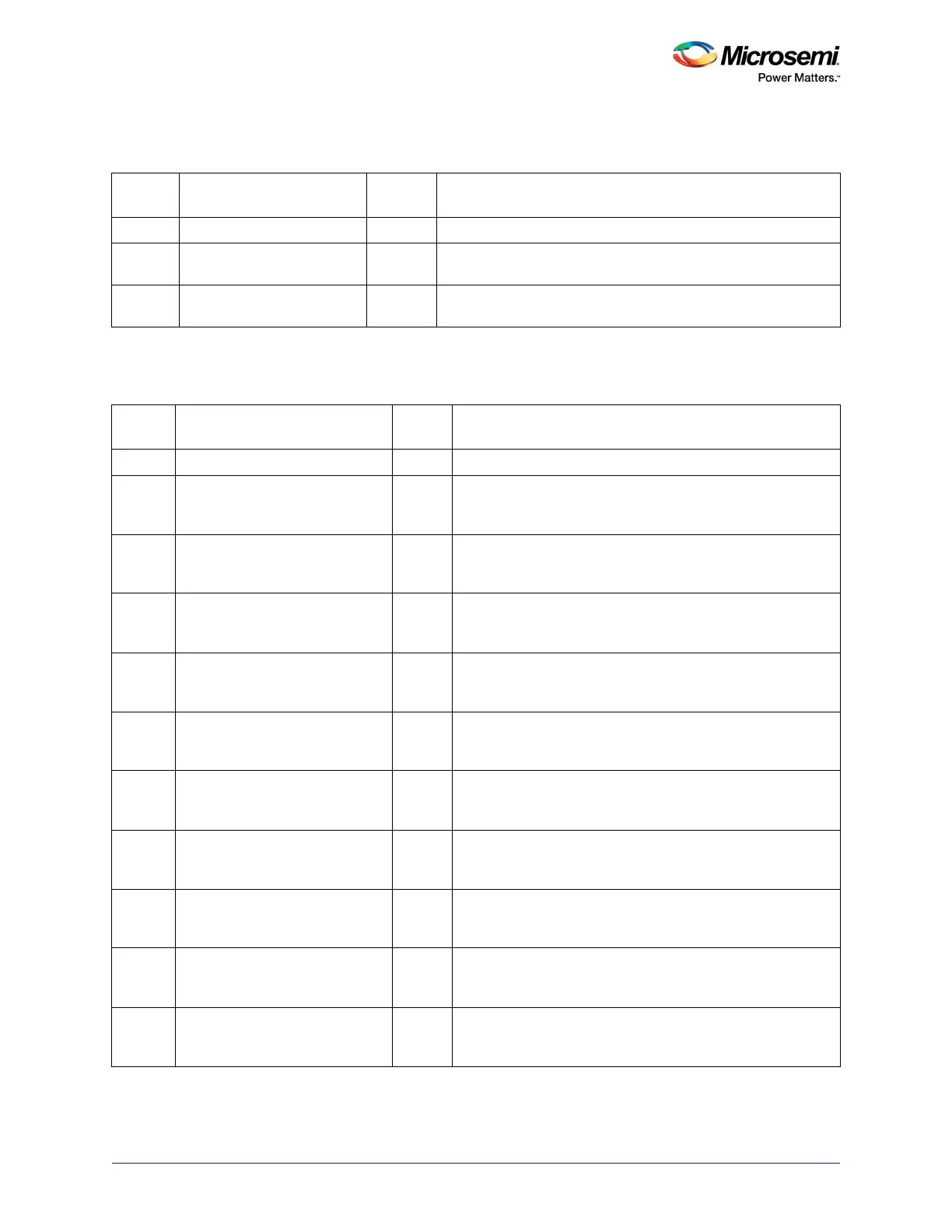

Table 131 • MM0_1_2_SECURITY

Bit

Number Name

Reset

Value Description

[31:10] Reserved 0 Reserved

9 MM0_1_2_MS6_ALLOWED_W 1 Write security bits for Masters 0, 1, and 2 to Slave 6 (MSS

DDR bridge). If not set, Masters 0, 1, and 2 will not have write

access to Slave 6.

8 MM0_1_2_MS6_ALLOWED_R 1 Read security bits for Masters 0, 1, and 2 to Slave 6 (MSS

DDR bridge). If not set, Masters 0, 1, and 2 will not have read

access to Slave 6.

7 MM0_1_2_MS3_ALLOWED_W 1 Write security bits for Masters 0, 1, and 2 to Slave 3 (eNVM1).

If not set, Masters 0, 1, and 2 will not have write access to

Slave 3.

6 MM0_1_2_MS3_ALLOWED_R 1 Read security bits for Masters 0, 1 and 2 to Slave 3 (eNVM1).

If not set, Masters 0, 1, and 2 will not have read access to

Slave 3.

5 MM0_1_2_MS2_ALLOWED_W 1 Write security bits for Masters 0, 1, and 2 to Slave 2 (eNVM0])

If not set, Masters 0, 1, and 2 will not have write access to

Slave 2.

4 MM0_1_2_MS2_ALLOWED_R 1 Read security bits for Masters 0, 1, and 2 to Slave 2 (eNVM0).

If not set, Masters 0, 1, and 2 will not have read access to

Slave 2.

3 MM0_1_2_MS1_ALLOWED_W 1 Write security bits for Masters 0, 1, and 2 to Slave 1

(eSRAM1). If not set, Masters 0, 1, and 2 will not have write

access to Slave 1.

2 MM0_1_2_MS1_ALLOWED_R 1 Read security bits for Masters 0, 1, and 2 to Slave 1

(eSRAM1). If not set, Masters 0, 1, and 2 will not have read

access to Slave 1.

1 MM0_1_2_MS0_ALLOWED_W 1 Write security bits for Masters 0, 1, and 2 to Slave 0

(eSRAM0). If not set, Masters 0, 1, and 2 will not have write

access to Slave 0.

0 MM0_1_2_MS0_ALLOWED_R 1 Read security bits for Masters 0, 1, and 2 to Slave 0

(eSRAM0). If not set, Masters 0, 1, and 2 will not have read

access to Slave 0.

Loading...

Loading...