System Register Block

UG0331 User Guide Revision 15.0 682

22.3 Register Details

22.3.1 System Registers Behavior for M2S005/010 Devices

Application traffic across the FIC_0 interface can cause certain bits in the SYSREG block to change

state, if these bits are dynamically modified from their default values during runtime. This impacts all

SmartFusion2 005 and 010 devices.

The following table lists the subset of system registers and specific bit definitions that are affected. The

registers/bits listed in the following table should be configured once on power-up. Dynamically altering

the contents of these registers can result in their values to be reset to the power on reset state.

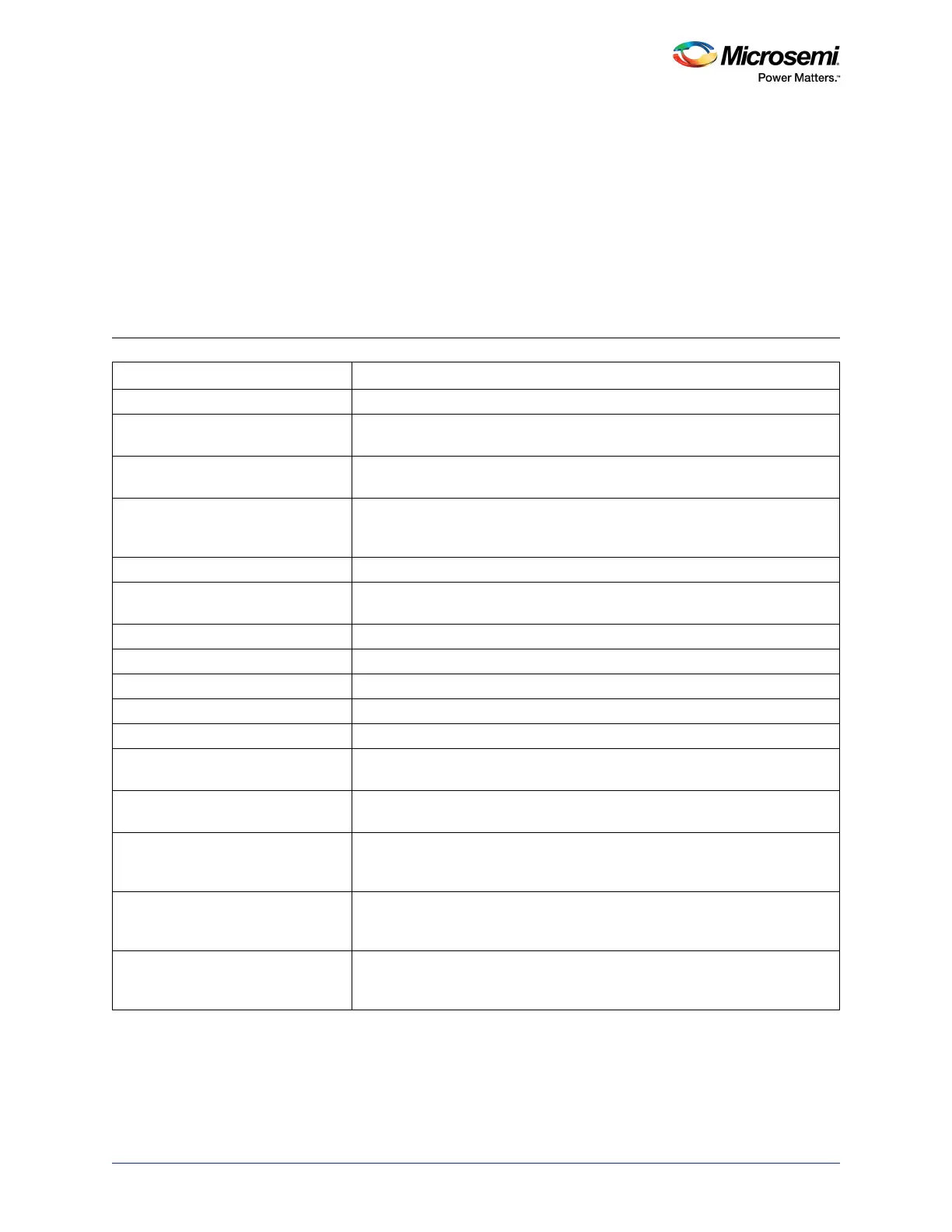

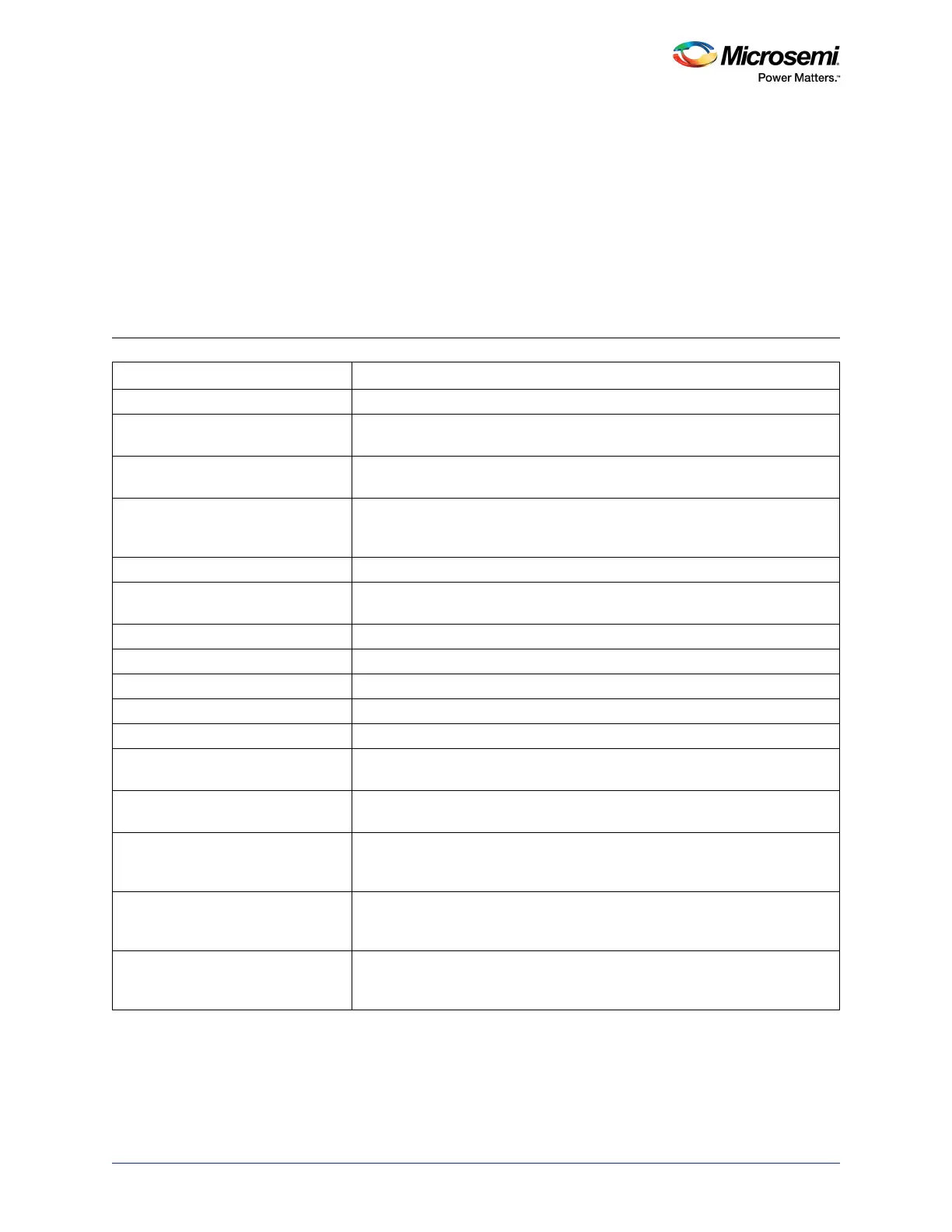

Table 651 • Subset of System Registers

System Register Fields

SOFT_RESET_CR All bits

M3_CR STCALIB

FAB_IF_CR FAB0_AHB_BYPASS, FAB1_AHB_BYPASS, FAB0_AHB_MODE,

FAB1_AHB_MODE, and SW_FIC_REG_SEL

LOOPBACK_CR MSS_MMUARTLOOPBACK, MSS_SPILOOPBACK, MSS_I2CLOOPBACK,

and MSS_GPIOLOOPBACK

GPIO_SYSRESET_SEL_CR MSS_GPIO_7_0_SYSRESET_SEL, MSS_GPIO_15_8_SYSRESET_SEL,

MSS_GPIO_23_16_SYSRESET_SEL, and

MSS_GPIO_31_24_SYSRESET_SEL

GPIN_SRC_SEL_CR MSS_GPINSOURCE

MDDR_CR MDDR_CONFIG_LOCAL, SDR_MODE, F_AXI_AHB_MODE, and

PHY_SELF_REF_EN

USB_IO_INPUT_SEL_CR USB_IO_INPUT_SEL

PERIPH_CLK_MUX_SEL_CR SPI0_SCK_FAB_SEL, SPI1_SCK_FAB_SEL, and TRACECLK_DIV2_SEL

WDOG_CR WDOGENABLE and WDOGMODE

EDAC_IRQ_ENABLE_CR All bits

MSS_IRQ_ENABLE_CR DDRB_INTERRUPT_EN, SW_INTERRUPT_EN, and CC_INTERRUPT_EN

RTC_WAKEUP_CR RTC_WAKEUP_M3_EN, RTC_WAKEUP_FAB_EN, and

RTC_WAKEUP_C_EN

MSSDDR_PLL_STATUS_LOW_CR FACC_PLL_DIVR, FACC_PLL_DIVF, FACC_PLL_DIVQ,

FACC_PLL_RANGE, FACC_PLL_LOCKWIN, and FACC_PLL_LOCKCNT

MSSDDR_PLL_STATUS_HIGH_CR FACC_PLL_BYPASS, FACC_PLL_MODE_1V2, FACC_PLL_MODE_3V3,

FACC_PLL_FSE, FACC_PLL_PD, FACC_PLL_SSE, FACC_PLL_SSMD, and

FACC_PLL_SSMF

MSSDDR_FACC1_CR DIVISOR_A, APB0_DIVISOR, APB1_DIVISOR, DDR_CLK_EN,

M3_CLK_DIVISOR, FACC_GLMUX_SEL, FIC_0_DIVISOR, and

FIC_1_DIVISOR

IOMUXCELL_CONFIG[n] MSS_IOMUXSEL0[N], MSS_IOMUXSEL1[N], MSS_IOMUXSEL2[N],

MSS_IOMUXSEL3[N], MSS_IOMUXSEL4[N][2:0], MSS_IOMUXSEL5MID[N],

and MSS_IOMUXSEL5LOWER[N]

Loading...

Loading...