Fabric Interface Interrupt Controller

UG0331 User Guide Revision 15.0 745

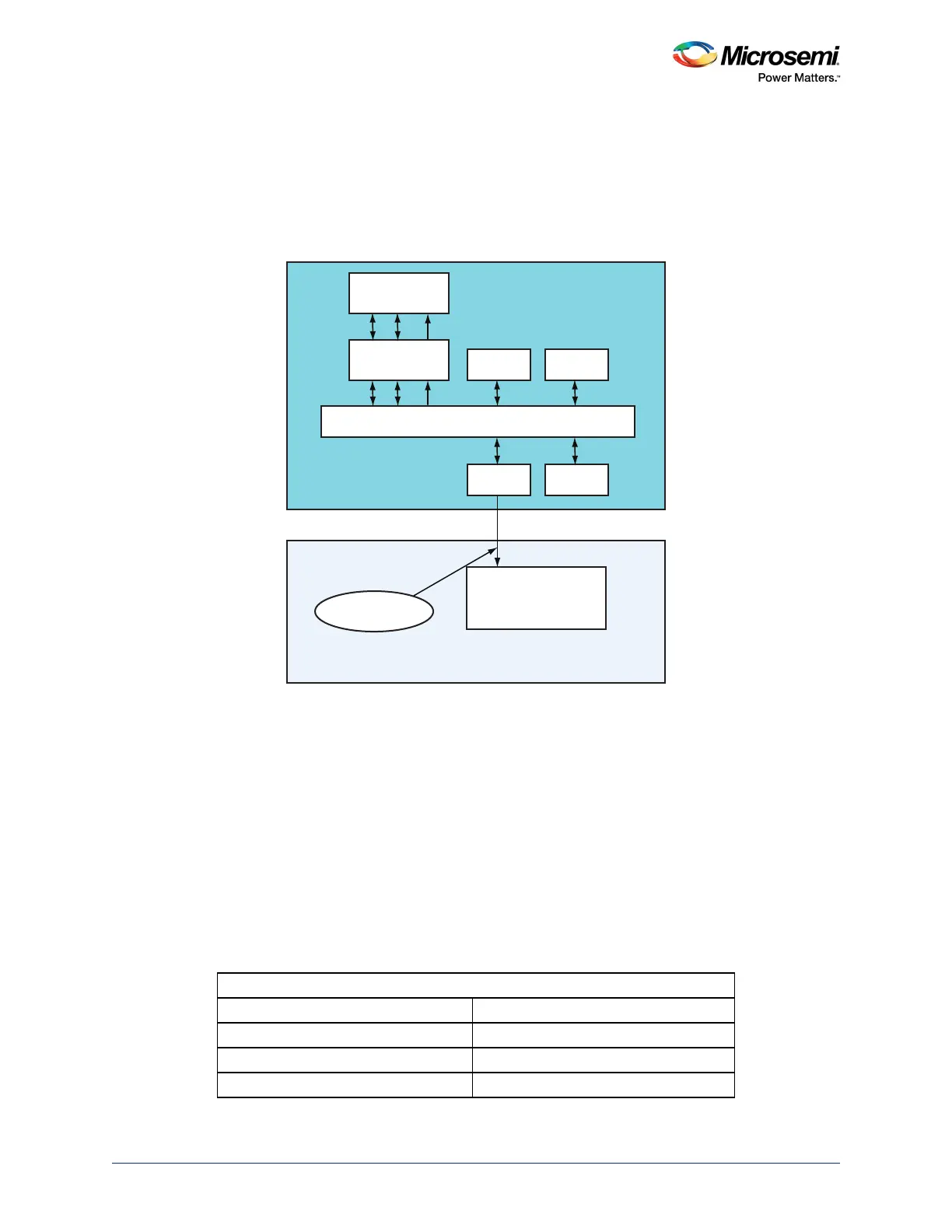

23.3.2.2 Use Model 2: MSS to the Fabric Interrupt

The following figure shows user logic in the fabric connectivity with the FIIC. You need to select Use MSS

to Fabric Interrupt in the Interrupt Management (FIIC) configurator in the Libero SoC. The

MSS_INT_M2F signals are then available to be used in the design.

The user logic can monitor these signals and process according to the application requirement. The

figure lists the MSS peripheral interrupts that correspond to the MSS_INT_M2F signals.

Figure 325 • MSS to Fabric Interrupt

23.3.2.2.1 Software Design Flow

The software design flow consists of enabling the MSS to the fabric interrupts.

Enabling the MSS to the Fabric interrupt

The interrupt enable registers do not affect the Cortex-M3 process or the NVIC; these are per bit enables

of the interrupt routed to the FPGA fabric. It enables the MSS to fabric interrupt, MSS_INT_M2F, by

setting the following INTERRUPT_ENABLE0 or INTERRUPT_ENABLE1 register bit-band.

INTERRUPT_CTRL_BITBAND-> bit-band register bit of INTERRUPT_ENABLE0 or

INTERRUPT_ENABLE1 = <1/0>;

The following table gives the bit-band register bit of INTERRUPT_ENABLE0 and

INTERRUPT_ENABLE1 in INTERRUPT_CTRL structure. Refer to m2sxxx.h contained in the CMSIS

folder.

Table 769 • Bit-Band Register Bit of Interrupt_Enable0 and Interrupt_Enable1

Bit-Band Register Bit

INTERRUPT_ENABLE0 INTERRUPT_ENABLE1

SPIINT0_ENBL RESERVED1[3]

SPIINT1_ENBL MDDR_IO_CALIB_INT_ENBL

I2C_INT0_ENBL RESERVED2

ARM Cortex-M3

Cache Controller

eNVMeSRAM

AHB Bus Matrix

FIIC FIC_X

User Logic

MSS

FPGA Fabric

MSS_INT_M2F

SD IS

SDICS

Loading...

Loading...