CAN Controller

UG0331 User Guide Revision 15.0 451

12.6 CAN Controller Register Map

12.6.1 SYSREG Control Registers

In addition to the specific CAN registers described in this chapter, the registers found in the CAN

SYSREG Control Registers also control the behavior of the CAN peripheral. Refer to the System

Register Block, page 670 for a detailed description of each register and bit.

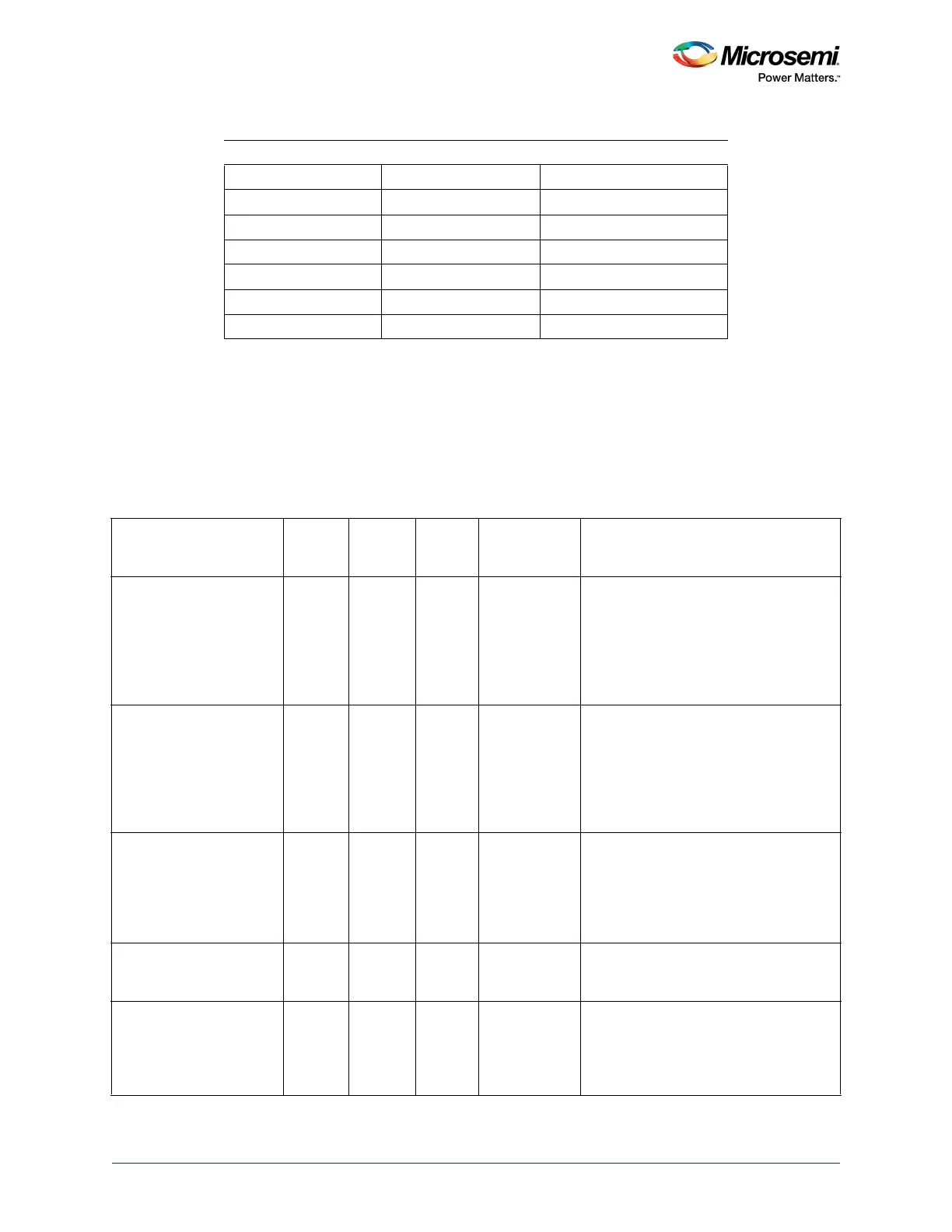

0x540-0x55C 0x148-0x14F Receive Message Object 25

0x560-0x57C 0x150-0x157 Receive Message Object 26

0x580-0x59C 0x158-0x15F Receive Message Object 27

0x5A0-0x5BC 0x160-0x167 Receive Message Object 28

0x5C0-0x5DC 0x168-0x16F Receive Message Object 29

0x5E0-0x5FC 0x170-0x177 Receive Message Object 30

0x600-0x61C 0x178-0x17F Receive Message Object 31

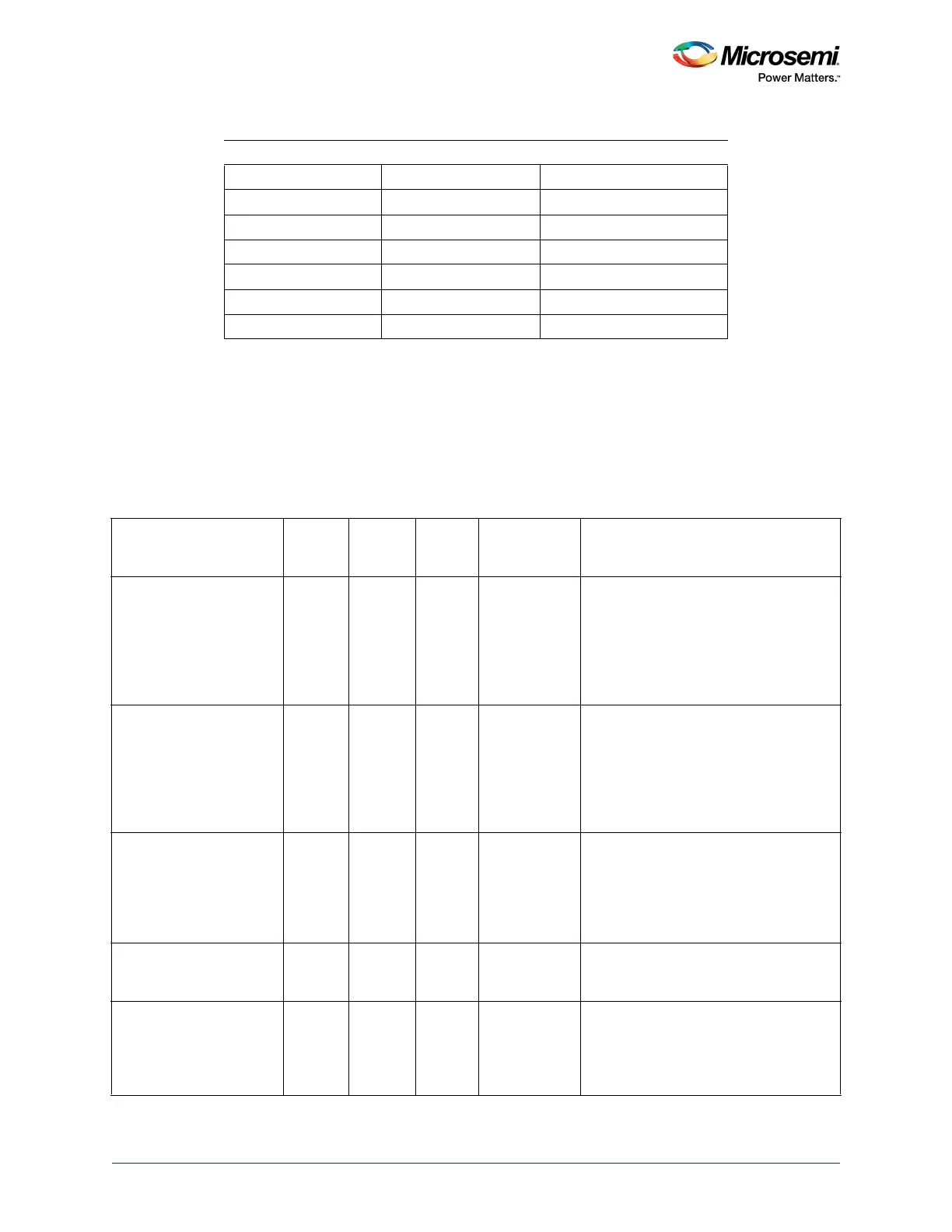

Table 439 • CAN SYSREG Control Registers

Register Name

Address

Offset

Register

Type

Flash

Write

Protect Reset Source Description

EDAC_CR 0x38 RW-P Register SYSRESET_N Configures EDAC component of the

CAN.

To enable or disable the EDAC for the

CAN, set the CAN_EDAC_EN bit (6th bit

in this register) as follows:

0: EDAC is disabled.

1: EDAC is enabled.

EDAC_IRQ_ENABLE_CR 0x78 RW-P Register SYSRESET_N Configures EDAC interrupts

To set 1-bit error or 2-bit error, set the

CAN_EDAC_1E_EN and

CAN_EDAC_2E_N bits (the 12th and

13th bits in this register)

0: Disables the status signal.

1: Enables the status signal.

CAN_EDAC_CNT 0x108 RO SYSRESET_N CAN EDAC count

This is a 16-bit counter value in CAN.

It is incremented by CAN EDAC 1-bit or

2-bit error.

The counter does not roll back and stays

at its max value.

CAN_EDAC_ADR 0x11C RO SYSRESET_N CAN EDAC address register

CAN memory address on which 1-bit or

2-bit SECDED error occurs.

EDAC_SR 0x190 SW1C SYSRESET_N EDAC status register

This status is updated by CAN when a

1-bit or 2-bit SECDED error has been

detected and a single-bit error is

corrected for RAM memory.

Table 438 • APB to SRAM Address Mapping (continued)

APB Address SRAM Address Description

Loading...

Loading...