System Register Block

UG0331 User Guide Revision 15.0 691

22.3.16 EDAC Configuration Register

22.3.17 Master Weight Configuration Register 0

2 DDRB_HPD_WEN 0x1 Allows the write combining buffer for high performance DMA master in MSS

DDR bridge to be disabled. Allowed values:

0: Disabled

1: Enabled

1 DDRB_DS_REN 0x1 Allows the read buffer for DSG master in MSS DDR bridge to be disabled.

Allowed values:

0: Disabled

1: Enabled

0 DDRB_DS_WEN 0x1 Allows write combining buffer for DSG master in MSS DDR bridge to be

disabled. Allowed values:

0: Disabled

1: Enabled

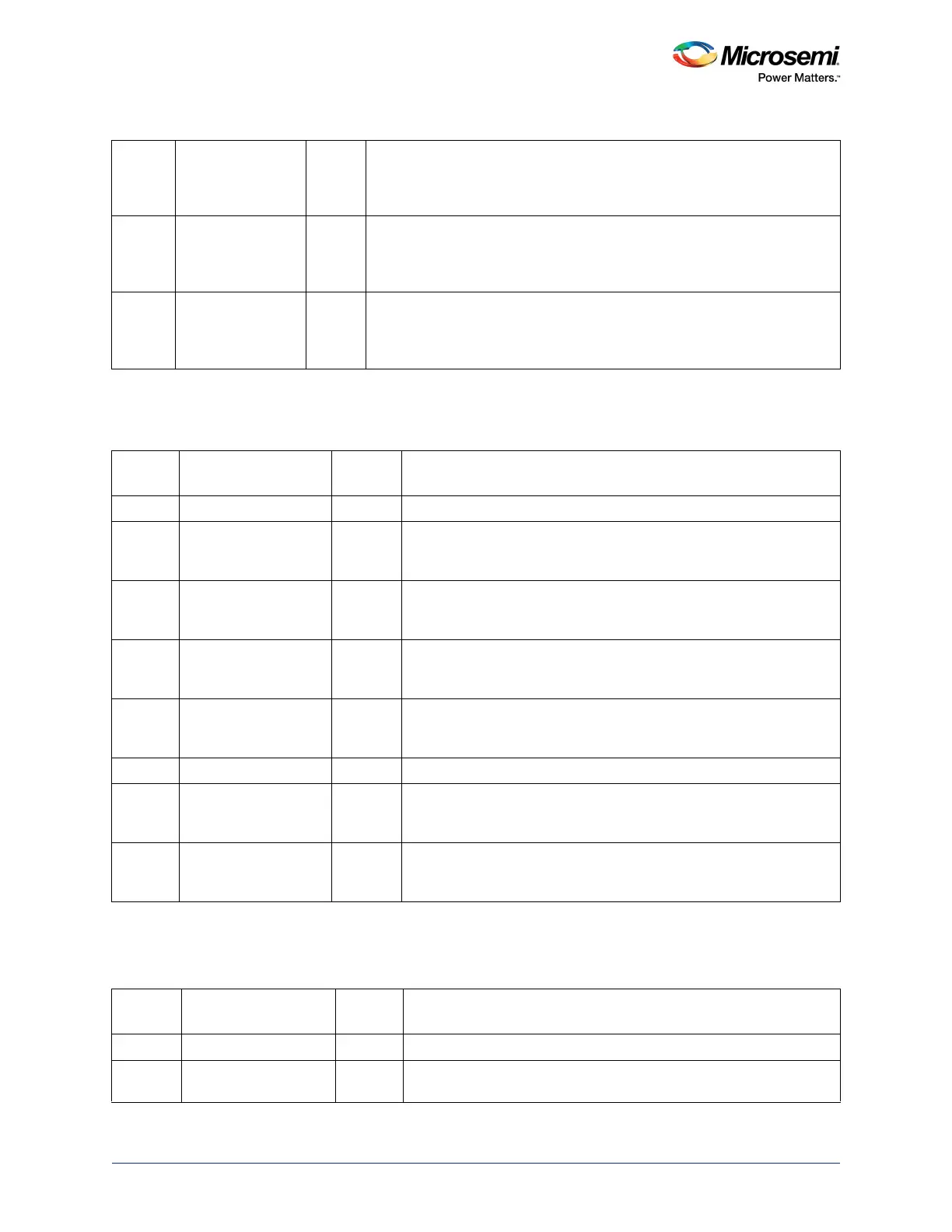

Table 669 • EDAC_CR

Bit

Number Name

Reset

Value Description

[31:7] Reserved 0

6 CAN_EDAC_EN 0 Allows the EDAC for CAN to be disabled. Allowed values:

0: Disabled

1: Enabled

5 USB_EDAC_EN 0 Allows the EDAC for USB to be disabled. Allowed values:

0: Disabled

1: Enabled

4 MAC_EDAC_RX_EN 0 Allows the EDAC for Ethernet Rx RAM to be disabled. Allowed values:

0: Disabled

1: Enabled

3 MAC_EDAC_TX_EN 0 Allows the EDAC for Ethernet Tx RAM to be disabled. Allowed values:

0: Disabled

1: Enabled

2 Reserved 0

1 ESRAM1_EDAC_EN 0 Allows the EDAC for eSRAM1 to be disabled. Allowed values:

0: Disabled

1: Enabled

0 ESRAM0_EDAC_EN 0 Allows the EDAC for eSRAM0 to be disabled. Allowed values:

0: Disabled

1: Enabled

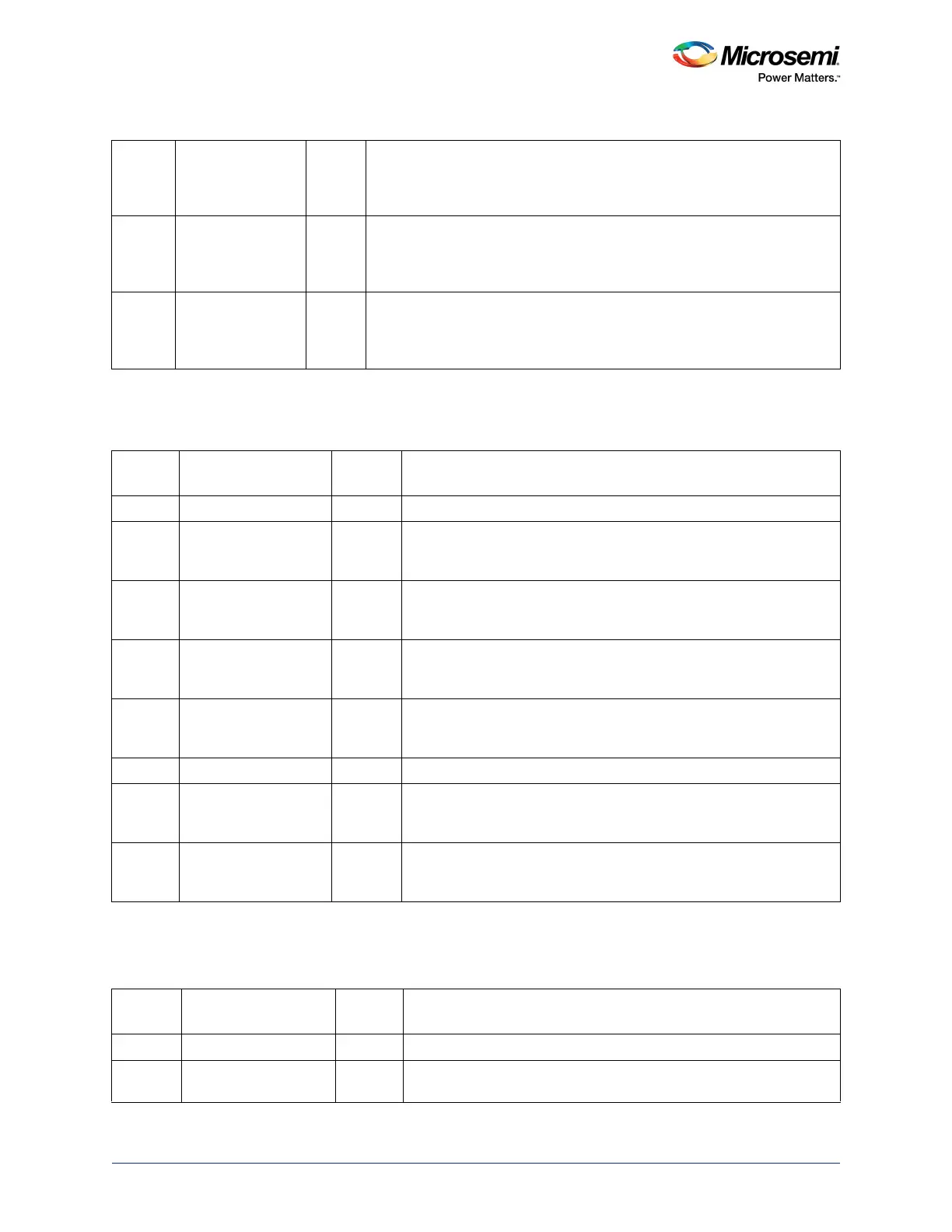

Table 670 • MASTER_WEIGHT0_CR

Bit

Number Name

Reset

Value Description

[31:30] Reserved 0

[29:25] SW_WEIGHT_PDMA 0 Configures the round robin weight for peripheral DMA master. It is

configurable from 1 to 32 (32 by default).

Table 668 • DDRB_CR (continued)

Loading...

Loading...