Embedded SRAM (eSRAM) Controllers

UG0331 User Guide Revision 15.0 206

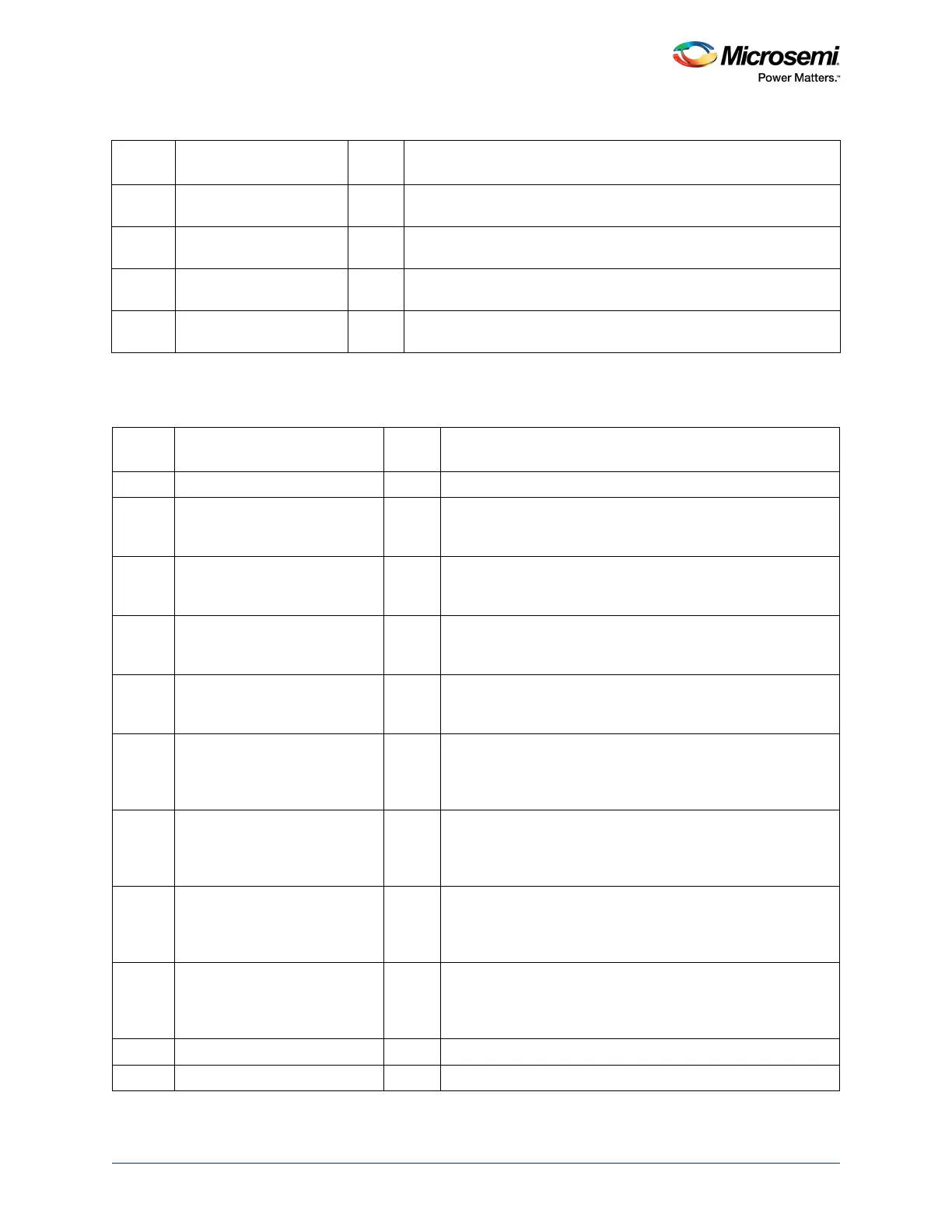

3 ESRAM1_EDAC_2E 0 Updated by the eSRAM_1 controller when a 2-bit SECDED error has

been detected for eSRAM1 memory.

2 ESRAM1_EDAC_1E 0 Updated by the eSRAM_1 Controller when a 1-bit SECDED error has

been detected and is corrected for eSRAM1 memory.

1 ESRAM0_EDAC_2E 0 Updated by the eSRAM_0 controller when a 2-bit SECDED error has

been detected for eSRAM0 memory.

0 ESRAM0_EDAC_1E 0 Updated by the eSRAM_0 controller when a 1-bit SECDED error has

been detected and is corrected for eSRAM0 memory.

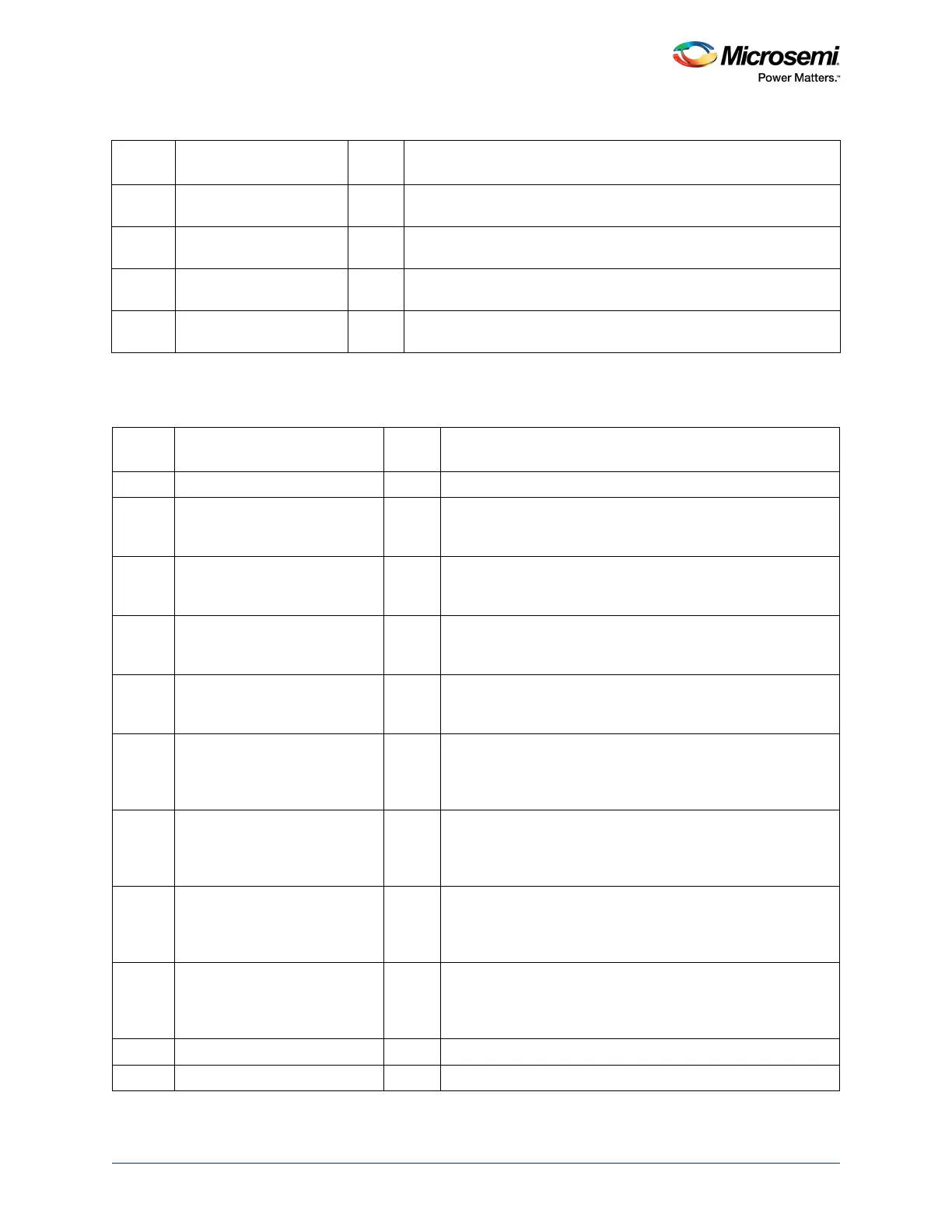

Table 136 • CLR_EDAC_COUNTERS

Bit

Number Name

Reset

Value Description

[31:14] Reserved 0 Reserved

13 CAN_EDAC_CNTCLR_2E 0 Generated to clear the 16-bit counter value in CAN

corresponding to the count value of EDAC 2-bit errors. This in

turn clears the upper 16 bits of the CAN_EDAC_CNT register.

12 CAN_EDAC_CNTCLR_1E 0 Generated to clear the 16-bit counter value in CAN

corresponding to the count value of EDAC 1-bit errors. This in

turn clears the lower 16 bits of the CAN_EDAC_CNT register.

11 USB_EDAC_CNTCLR_2E 0 Generated to clear the 16-bit counter value in USB

corresponding to the count value of EDAC 2-bit errors. This in

turn clears the upper 16 bits of the USB_EDAC_CNT register.

10 USB_EDAC_CNTCLR_1E 0 Generated to clear the 16-bit counter value in USB

corresponding to the count value of EDAC 1-bit errors. This in

turn clears the lower 16 bits of the USB_EDAC_CNT register.

9 MAC_EDAC_RX_CNTCLR_2E 0 Generated to clear the 16-bit counter value in Ethernet MAC Rx

RAM corresponding to the count value of EDAC 2-bit errors.

This in turn clears the upper 16 bits of the

MAC_EDAC_RX_CNT register.

8 MAC_EDAC_RX_CNTCLR_1E 0 Generated to clear the 16-bit counter value in Ethernet MAC Rx

RAM corresponding to the count value of EDAC 1-bit errors.

This in turn clears the lower 16 bits of the

MAC_EDAC_RX_CNT register.

7 MAC_EDAC_TX_CNTCLR_2E 0 Generated to clear the 16-bit counter value in Ethernet MAC Tx

RAM corresponding to the count value of EDAC 2-bit errors.

This in turn clears the upper 16 bits of the

MAC_EDAC_TX_CNT register.

6 MAC_EDAC_TX_CNTCLR_1E 0 Generated to clear the 16-bit counter value in Ethernet MAC Tx

RAM corresponding to the count value of EDAC 1-bit errors.

This in turn clears the lower 16 bits of the

MAC_EDAC_TX_CNT register.

5 Reserved 0 Reserved

4 Reserved 0 Reserved

Table 135 • EDAC_SR (continued)

Bit

Number Name

Reset

Value Description

Loading...

Loading...