Ethernet MAC

UG0331 User Guide Revision 15.0 415

Table 370 • FIFO_RAM_ACCESS1

Bit Number Name Reset Value Description

[31:0] hsttramwdat 0x0 Host transmit RAM write data

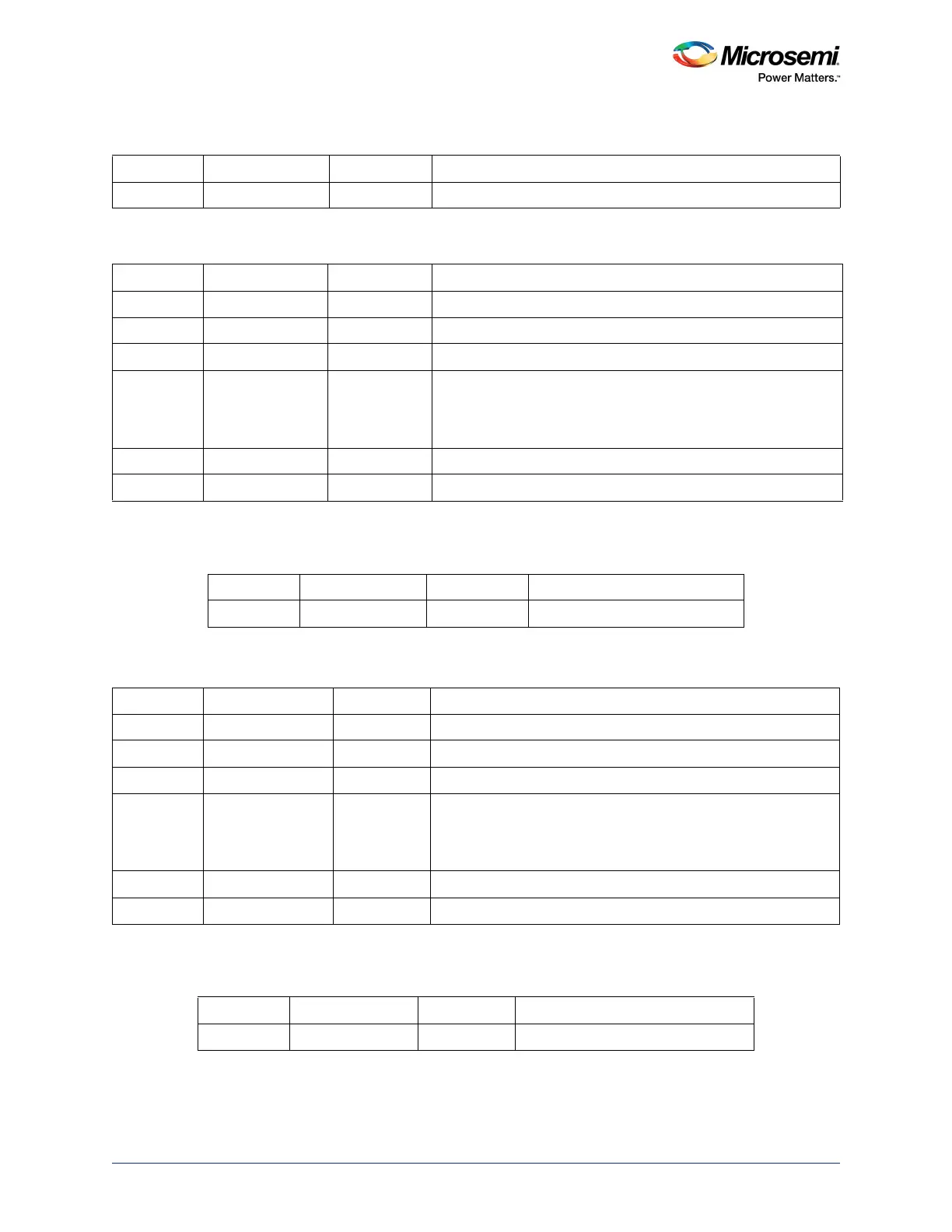

Table 371 • FIFO_RAM_ACCESS2

Bit Number Name Reset Value Description

31 hsttramrreq 0x0 Host transmit RAM read request

30 hsttramrack 0x0 Host transmit RAM read acknowledge

[29:24] Reserved 0x0 Reserved

[23:16] hsttramrdat 0x0 Host transmit RAM read data.

This is the upper byte of the transmit FIFO RAM data that was

read at the address of the hsttramwadx[10:0], if the

hsttramwadx[12] is negated and the hsttramwreq is asserted.

[15:13] Reserved 0x0 Reserved

[12:0] hsttramradx 0x0 Host transmit RAM read address

Table 372 • FIFO_RAM_ACCESS3

Bit Number Name Reset Value Description

[31:0] hsttramrdat 0x0 Host transmit RAM read data

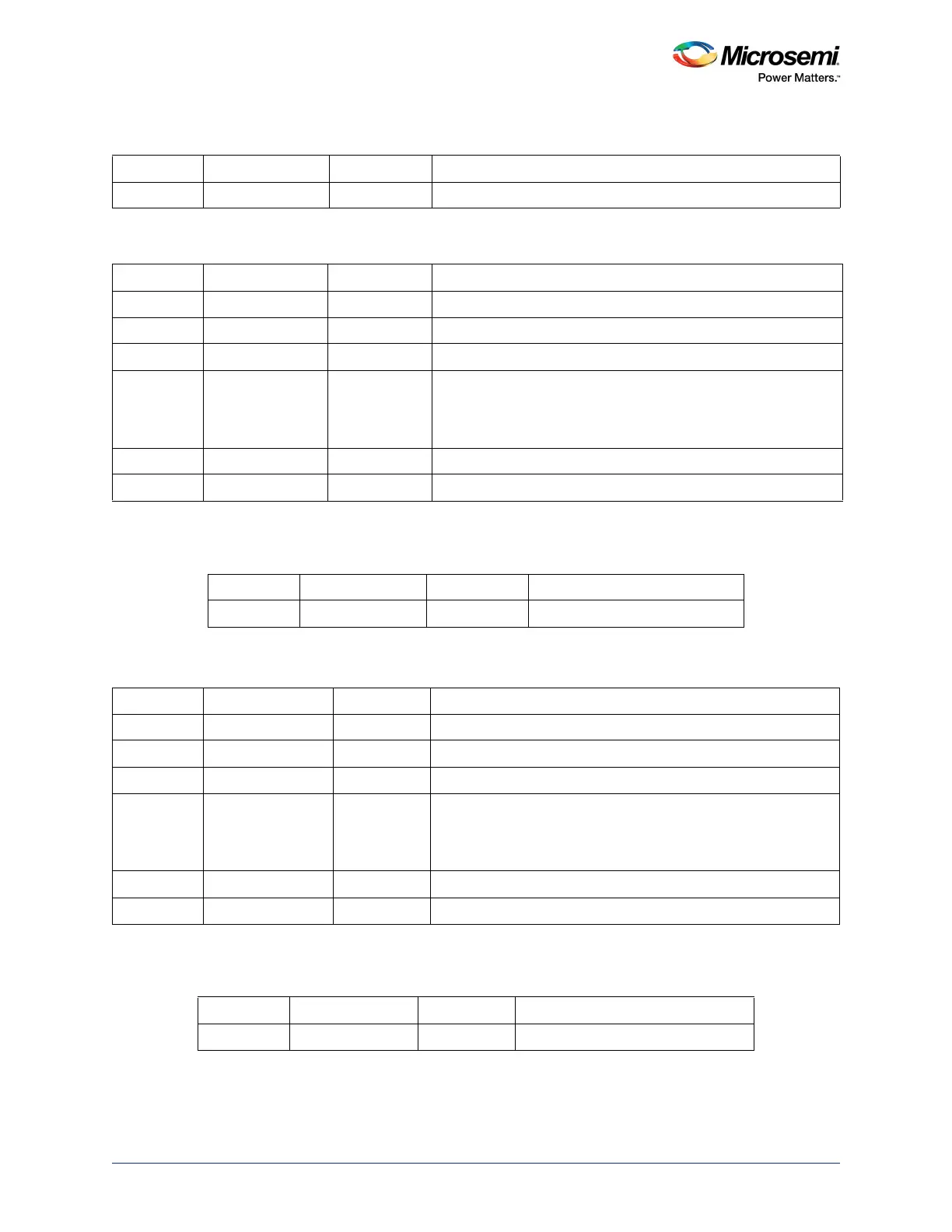

Table 373 • FIFO_RAM_ACCESS4

Bit Number Name Reset Value Description

31 hstrramwreq 0x0 Host receive RAM write request

30 hstrramwack 0x0 Host receive RAM write acknowledge

[29:24] Reserved 0x0 Reserved

[23:16] hstrramwdat[39:32] 0x0 Host receive RAM write data

This is the upper byte of the receive FIFO RAM data that is

written at the address of the hstrramwadx[11:0], if the

hstrramwadx[13] is negated and the hstrramwreq is asserted.

[15:14] Reserved 0x0 Reserved

[13:0] hsttramwadx 0x0 Host receive RAM write address

Table 374 • FIFO_RAM_ACCESS5

Bit Number Name Reset Value Description

[31:0] hstrramwdat 0x0 Host receive RAM write data

Loading...

Loading...