Fabric Interface Interrupt Controller

UG0331 User Guide Revision 15.0 746

To enable the MSS to the fabric interrupts, listed in the Select Group 0 or Select Group 1 column of

Table 766, page 740, set the bit-band register bit of INTERRUPT_MODE register as given below:

INTERRUPT_CTRL_BITBAND-> SELECT_MODE= <1/0>

;

Monitoring the MSS to the Fabric Interrupt Status

The status of the MSS to the fabric interrupt, MSS_INT_M2F, can be monitored by reading the bit-band

register bit of INTERRUPT_REASON0 and INTERRUPT_REASON1, as given below:

INTERRUPT_CTRL_BITBAND-> bit-band register bit of INTERRUPT_REASON0 or

INTERRUPT_REASON1;

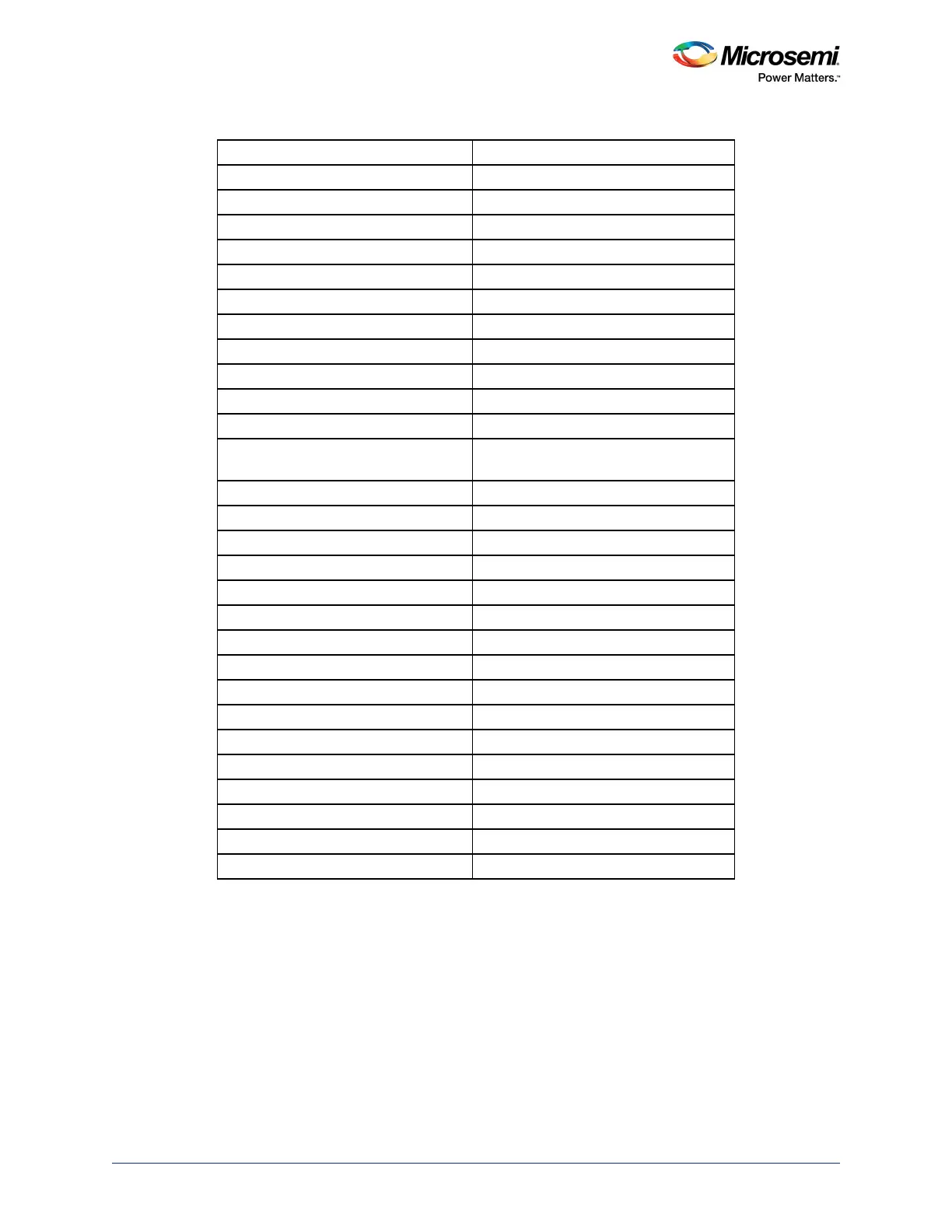

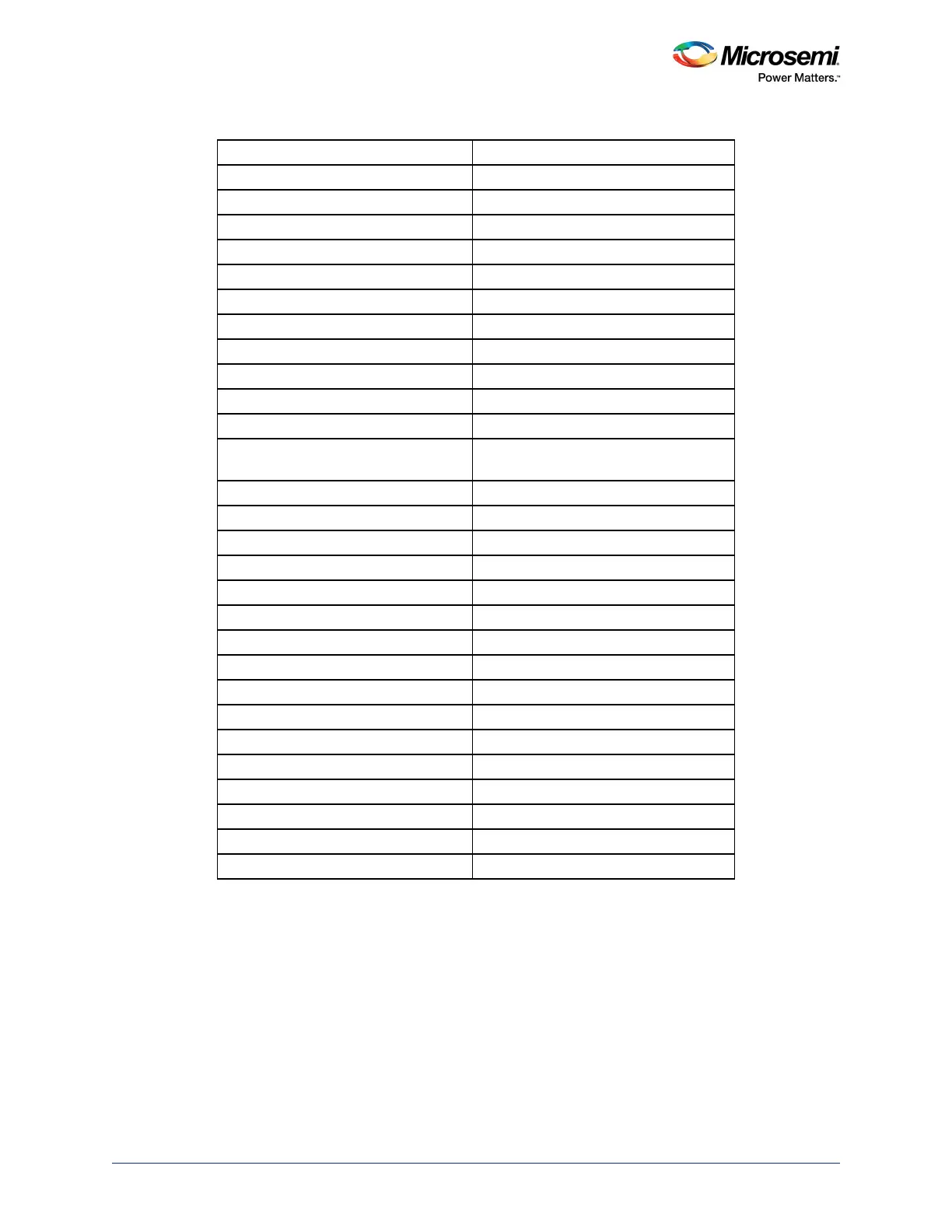

I2C_INT1_ENBL FAB_PLL_LOCK_INT_ENBL

MMUART0_INTR_ENBL FAB_PLL_LOCKLOST_INT_ENBL

MMUART1_INTR_ENBL FIC64_INT_ENBL

MAC_INT_ENBL RESERVED3[24]

USB_MC_INT_ENBL

PDMAINTERRUPT_ENBL

HPD_XFR_CMP_INT_ENBL

TIMER1_INTR_ENBL

TIMER2_INTR_ENBL

CAN_INTR_ENBL

RTC_WAKEUP_INTR_ENBL

WDOGWAKEUPINT_ENBL

MSSDDR_PLL_LOCKLOST_INT_ENB

L

ENVM_INT0_ENBL

ENVM_INT1_ENBL

I2C_SMBALERT0_ENBL

I2C_SMBSUS0_ENBL

I2C_SMBALERT1_ENBL

I2C_SMBSUS1_ENBL

HPD_XFR_ERR_INT_ENBL

MSSDDR_PLL_LOCK_INT_ENBL

SW_ERRORINTERRUPT_ENBL

DDRB_INTR_ENBL

ECCINTR_ENBL

CACHE_ERRINTR_ENBL

SOFTINTERRUPT_ENBL

COMBLK_INTR_ENBL

USB_DMA_INT_ENBL

RESERVED0

Table 769 • Bit-Band Register Bit of Interrupt_Enable0 and Interrupt_Enable1 (continued)

Loading...

Loading...