Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 330

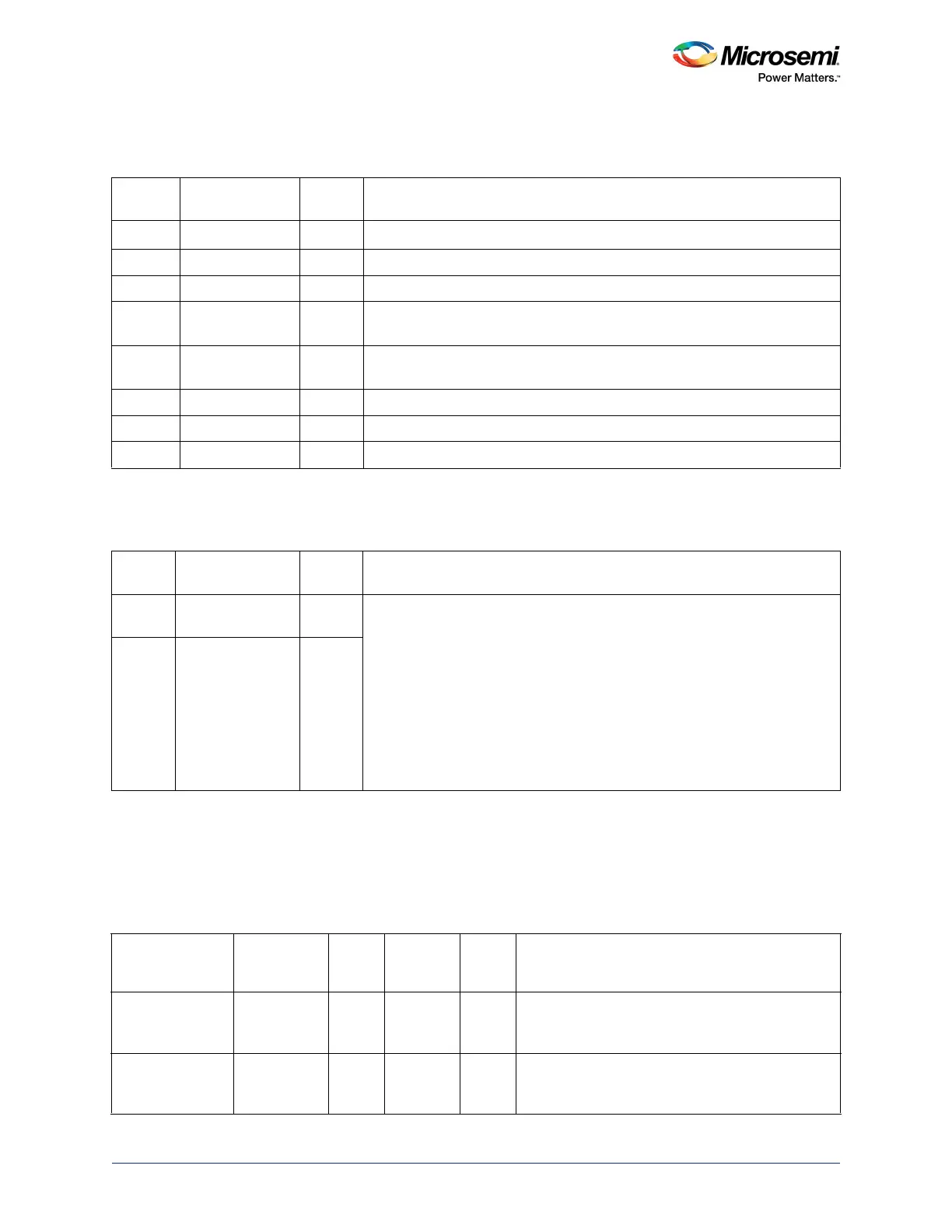

10.3.6.25 CONFIG_DATA_REG Bit Definitions

10.3.6.26 FIFO_SIZE_REG Bit Definitions

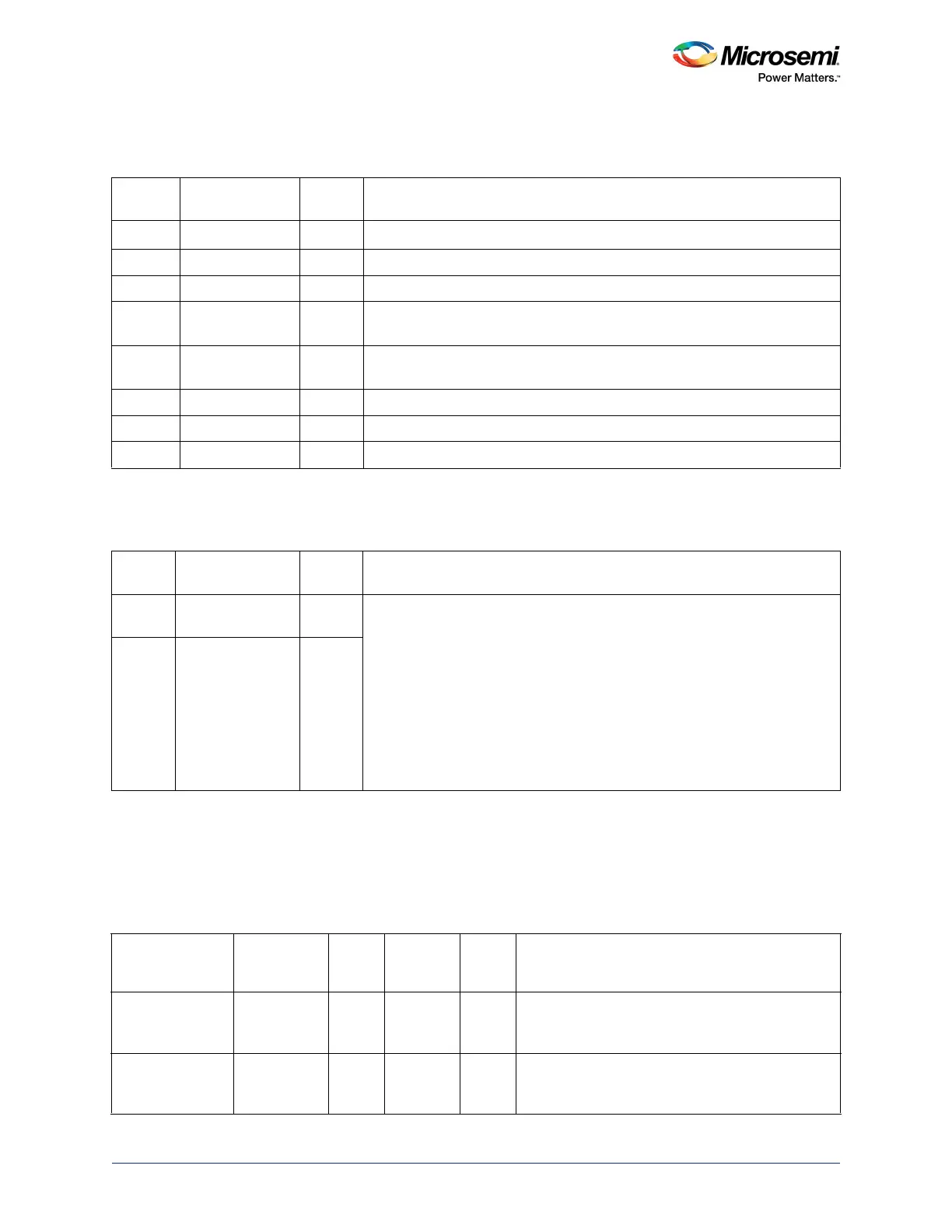

10.3.7 FIFO Registers

These registers provide access to endpoint transmit and receive FIFOs. Writing to these addresses loads

data into the transmit for the corresponding endpoint. Reading from these addresses unloads data from

the receive FIFO for the corresponding endpoint.

Table 236 • CONFIG_DATA_REG

Bit

Number Name

Reset

Value Function

7 MPRxE N/A When set to 1, automatic amalgamation of bulk packets is selected.

6 MPTxE N/A When set to 1, automatic splitting of bulk packets is selected.

5 BigEndian N/A Always 0. Indicates Little Endian ordering.

4 HBRxE N/A When set to 1, indicates high-bandwidth receive ISO endpoint support

selected.

3 HBTxE N/A When set to 1, indicates high-bandwidth transmit ISO endpoint support

selected.

2 DynFIFO Sizing N/A When set to 1, indicates dynamic FIFO sizing option selected.

1 SoftConE N/A Always 1. Indicates soft connect/disconnect.

0 UTMI DataWidth N/A Indicates selected UTMI+ data width. Always 0, indicating 8 bits.

Table 237 • FIFO_SIZE_REG

Bit

Number Name

Reset

Value Function

[7:4] Rx FIFO Size N/A Returns the sizes of the FIFOs associated with the selected additional

transmit/receive endpoints. The lower nibble, [3:0], encodes the size of the

selected transmit endpoint FIFO; the upper nibble, [7:4], encodes the size of

the selected receive endpoint FIFO. Values of 3 – 13 correspond to a FIFO

size of 2n bytes (8 – 8,192 bytes). If an endpoint has not been configured, a

value of 0 is displayed. When the transmit and receive endpoints share the

same FIFO, the Rx FIFO size will be encoded as 0xF.

The register only has this interpretation when the Index register is set to

select one of endpoints 1 – 15 and dynamic sizing is not selected. It has a

special interpretation when the INDEX_REG is set to select endpoint0; the

result returned is not valid where dynamic FIFO sizing is used.

[3:0] Tx FIFO Size N/A

Table 238 • FIFO Registers

Register Name

Address

Offset from

0x40043000 Width R/W Type

Reset

Value Description

EP0_FIFO_REG 0x0020 32 RW 0 Writing to this address loads data into the endpoint0

transmit FIFO. Reading from this address unloads

data from the endpoint0 transmit FIFO.

EP1_FIFO_REG 0x0024 32 RW 0 Writing to this address loads data into the endpoint1

transmit FIFO. Reading from this address unloads

data from the endpoint1 transmit FIFO.

Loading...

Loading...