CAN Controller

UG0331 User Guide Revision 15.0 457

The rest of the transmit message buffers (TX_MSG1 to TX_MSG31) registers and registers bits have the

same descriptions as the TX_MSG0 registers shown above.

0 TxReq 0 Transmit request; Command flag bit

Write:

0: Idle. No message transmit request.

1: Message transmit request

The Tx message buffer must not be changed while TxReq is 1.

Read:

0: TxReq completed

1: TxReq pending

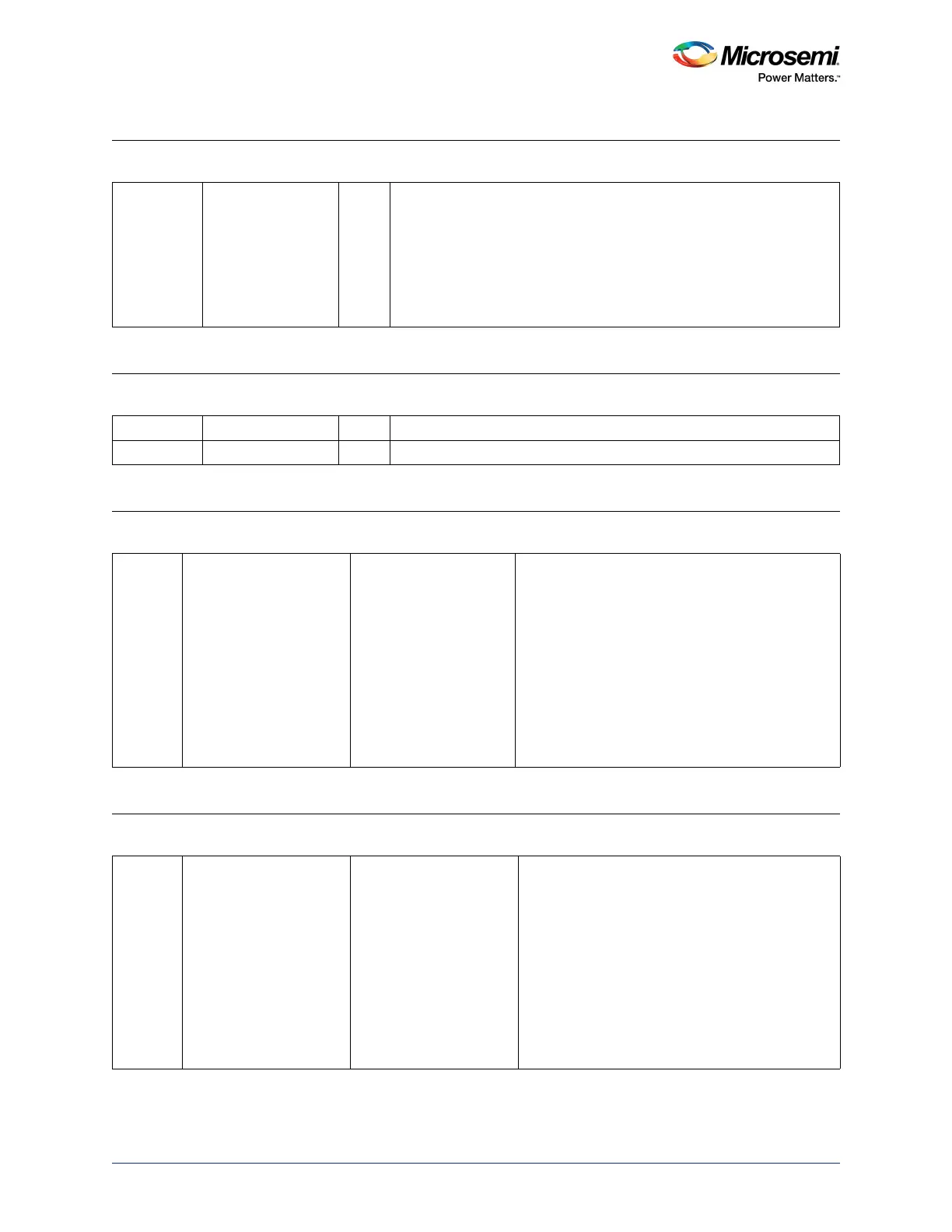

Table 445 • TX_MSG0_ID

Bit Number Name

Reset

Value Description

[31:3] ID[28:0] 0 Transmit message0 buffer identifier (29-bit wide)

[2:0] Reserved 0 Reserved

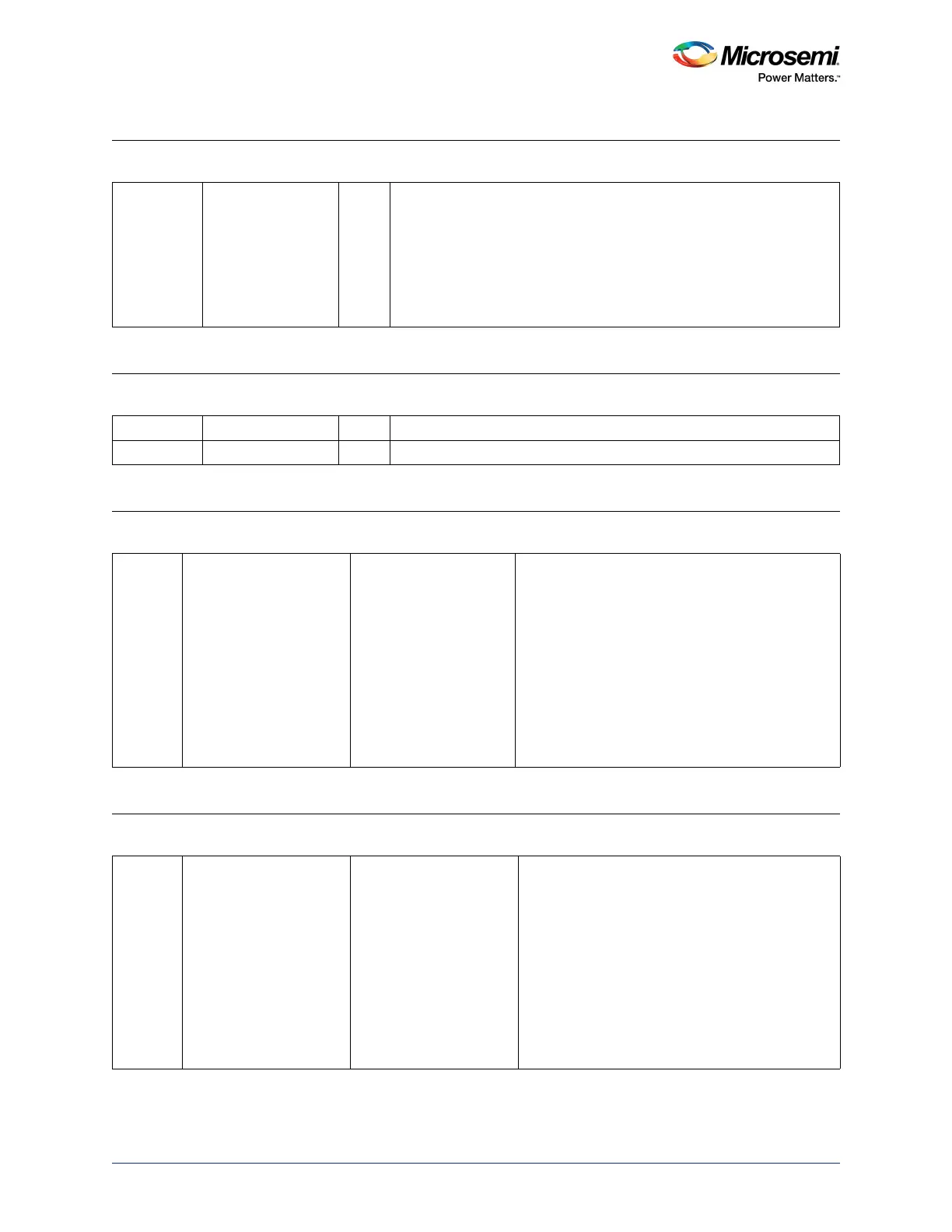

Table 446 • TX_MSG0_DATA_HIGH

Bit

Number Name Reset Value Description

[31:0] TX_MSG0_DATA_HIGH [31:24]: CAN data byte 1

[23:16]: CAN data byte 2

[15:8]: CAN data byte 3

[7:0]: CAN data byte 4

The byte mapping can be set using the CAN

swap_endian configuration bit.

swap_endian = 0, default

[31:24]: CAN data byte 1

[23:16]: CAN data byte 2

[15:8]: CAN data byte 3

[7:0]: CAN data byte 4

swap_endian = 1

[31:24]: CAN data byte 4

[23:16]: CAN data byte 3

[15:8]: CAN data byte 2

[7:0]: CAN data byte 1

Table 447 • TX_MSG0_DATA_LOW

Bit

Number Name Reset Value Description

[31:0] TX_MSG0_DATA_LOW [31:24]: CAN data byte 5

[23:16]: CAN data byte 6

[15:8]: CAN data byte 7

[7:0]: CAN data byte 8

The byte mapping can be set using the CAN

swap_endian configuration bit

swap_endian = 0, default

[31:24]: CAN data byte 5

[23:16]: CAN data byte 6

[15:8]: CAN data byte 7

[7:0]: CAN data byte 8

swap_endian = 1

[31:24]: CAN data byte 8

[23:16]: CAN data byte 7

[15:8]: CAN data byte 6

[7:0]: CAN data byte 5

Table 444 • TX_MSG0_CTRL_CMD (continued)

Bit Number Name

Reset

Value Description

Loading...

Loading...