Embedded NVM (eNVM) Controllers

UG0331 User Guide Revision 15.0 149

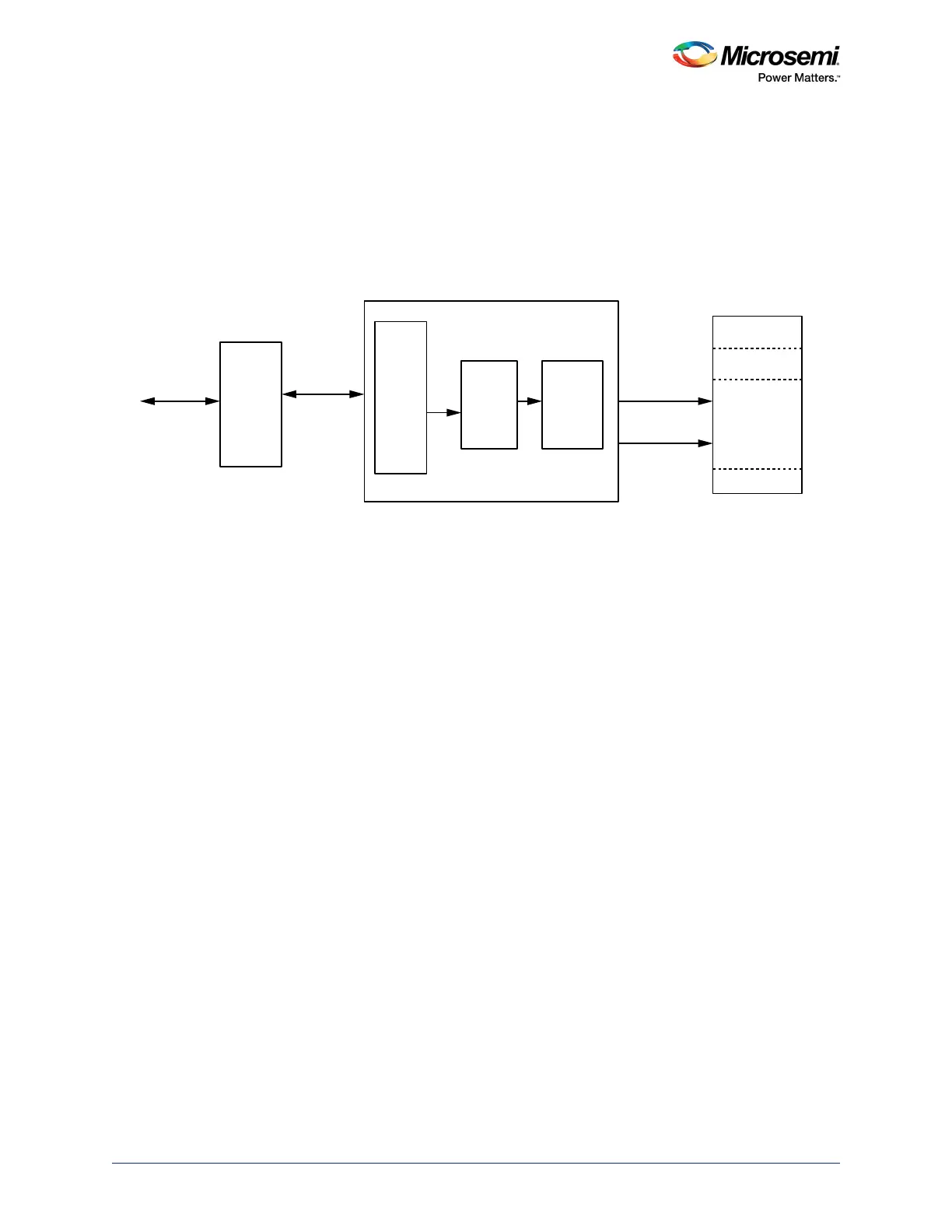

Figure 67 • Write Path

5.2.4.2 Read Control

The following steps describe eNVM read control.

• The read transaction from the eNVM user array to AHBL bus uses the read data buffer as a mini

cache.

• If the requested 32-bit word exists in the read data buffer, it will be returned immediately on the AHB

bus; otherwise a 64-bit read access of the eNVM is initiated and will take several clock cycles as

configured by ENVM_CR register.

• The eNVM data is stored in the read data buffer and provided to the AHB bus. Assuming that the

eNVM address is incremented, the data value stored in the read data buffer is available for the next

AHB read cycle.

6HFWRU

6HFWRUQ

6HFWRUQ

H190WR

$+%

&RQWUROOHU

H190$UUD\

$+%/,QWHUIDFH

H190&RQWUROOHU

(&&

:ULWH

'DWD

%XIIHU

$VVHPEO\

%XIIHU

&RPPDQGVDQG

%LW'DWD

,QWHUIDFH

$GGUHVV,QWHUIDFH

:ULWHGDWD

%LW

%LW

Loading...

Loading...