Ethernet MAC

UG0331 User Guide Revision 15.0 430

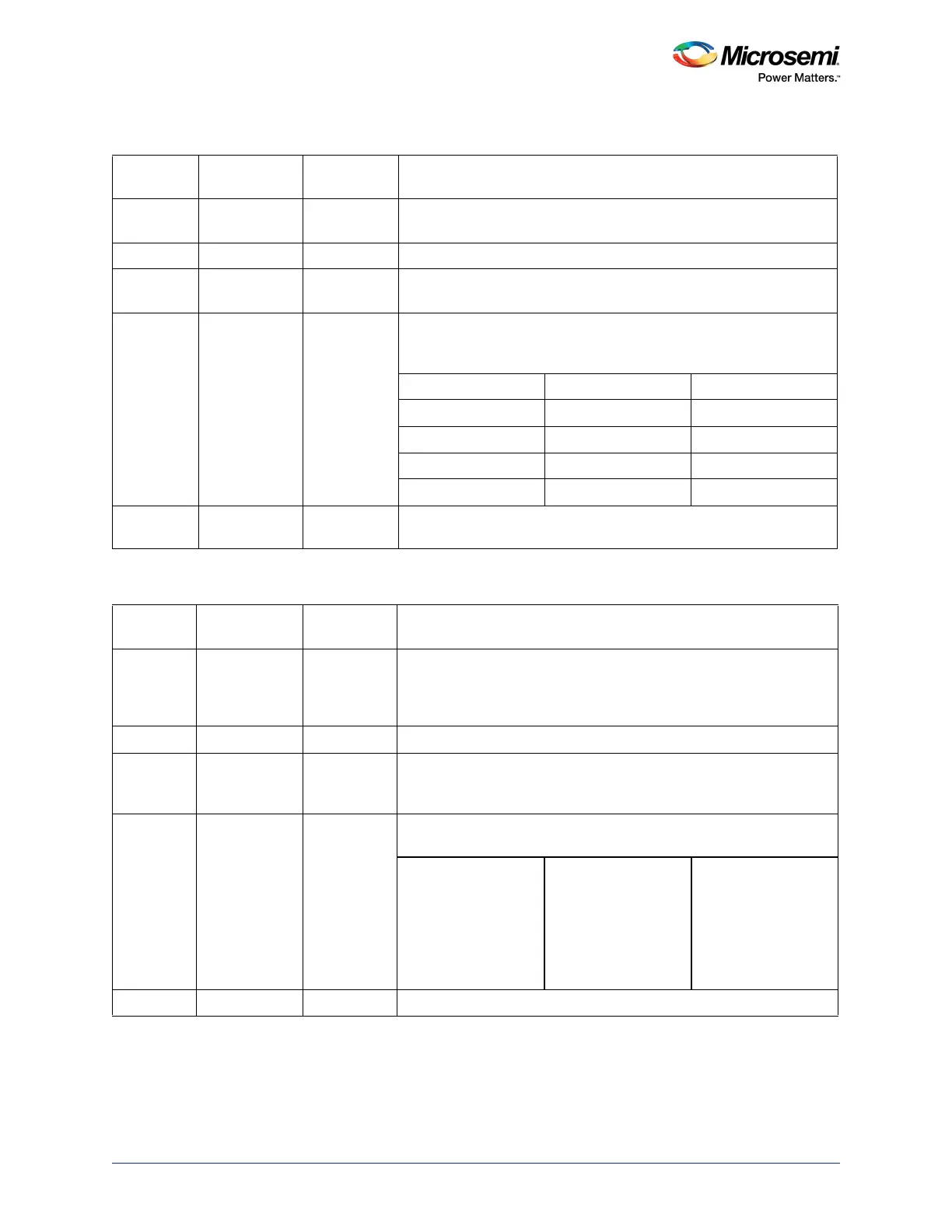

Table 427 • AN SGMII ADVERTISEMENT

Bit Number Name Reset Value Description

15 LINK UP 0x0 Assertion of this bit indicates that the link between M-SGMII and PHY

is up.

[14:13] Reserved 0x0 Reserved.

12 FULL DUPLEX 0x0 Assertion of this bit indicates that the link between M-SGMII and PHY

is up and transferring data in Full-duplex mode.

[11:10] LINK SPEED 0x0 Assertion of these 2 bits indicate that the link between M-SGMII and

PHY is up and the speed that the link is transferring data is as

mentioned below:

LINK SPEED [11] LINK SPEED [10] Capability

11Reserved

1 0 1000 Mbps

0 1 100 Mbps

0 0 10 Mbps

[9:0] Reserved 0x0 These bits must always be written ‘0000000001’ for correct M-SGMII

operation.

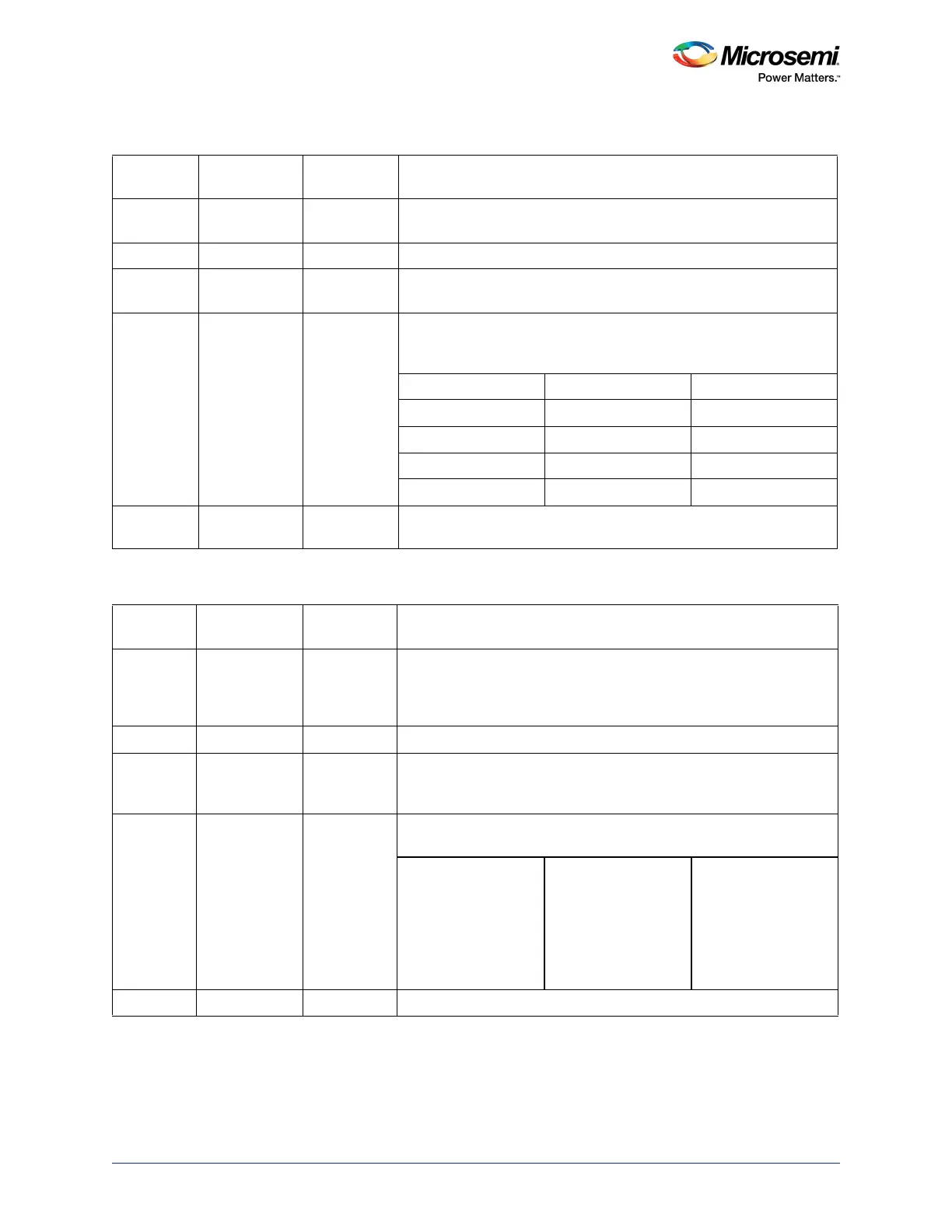

Table 428 • AN LINK PARTNER BASE PAGE ABILITY

Bit Number Name Reset Value Description

15 LINK UP 0x0 When the M-SGMII is integrated to a MAC, such as the PE-MCXMAC,

and is communicating with another SGMII PHY module, assertion of

this bit indicates that the link is up. When the M-SGMII is integrated to

a PHY and is not integrated to MAC, this bit is invalid.

[14:13] Reserved 0x0 Reserved.

12 FULL DUPLEX 0x0 Assertion of this bit indicates that LINK UP bit of the AN SGMII partner

base page ability register is asserted and the link is transferring data in

full-duplex mode.

[11:10] LINK SPEED 0x0 Indicates the speed of the link as mentioned below when LINK UP bit

of the AN SGMII partner base page ability register is asserted.

LINK SPEED [11] LINK SPEED [10] Capability

11Reserved

1 0 1000 Mbps

0 1 100 Mbps

0 0 10 Mbps

[9:0] Reserved 0x0 Reserved

Loading...

Loading...