High Performance DMA Controller

UG0331 User Guide Revision 15.0 262

8.4.1.23 HPDMA Debug Register

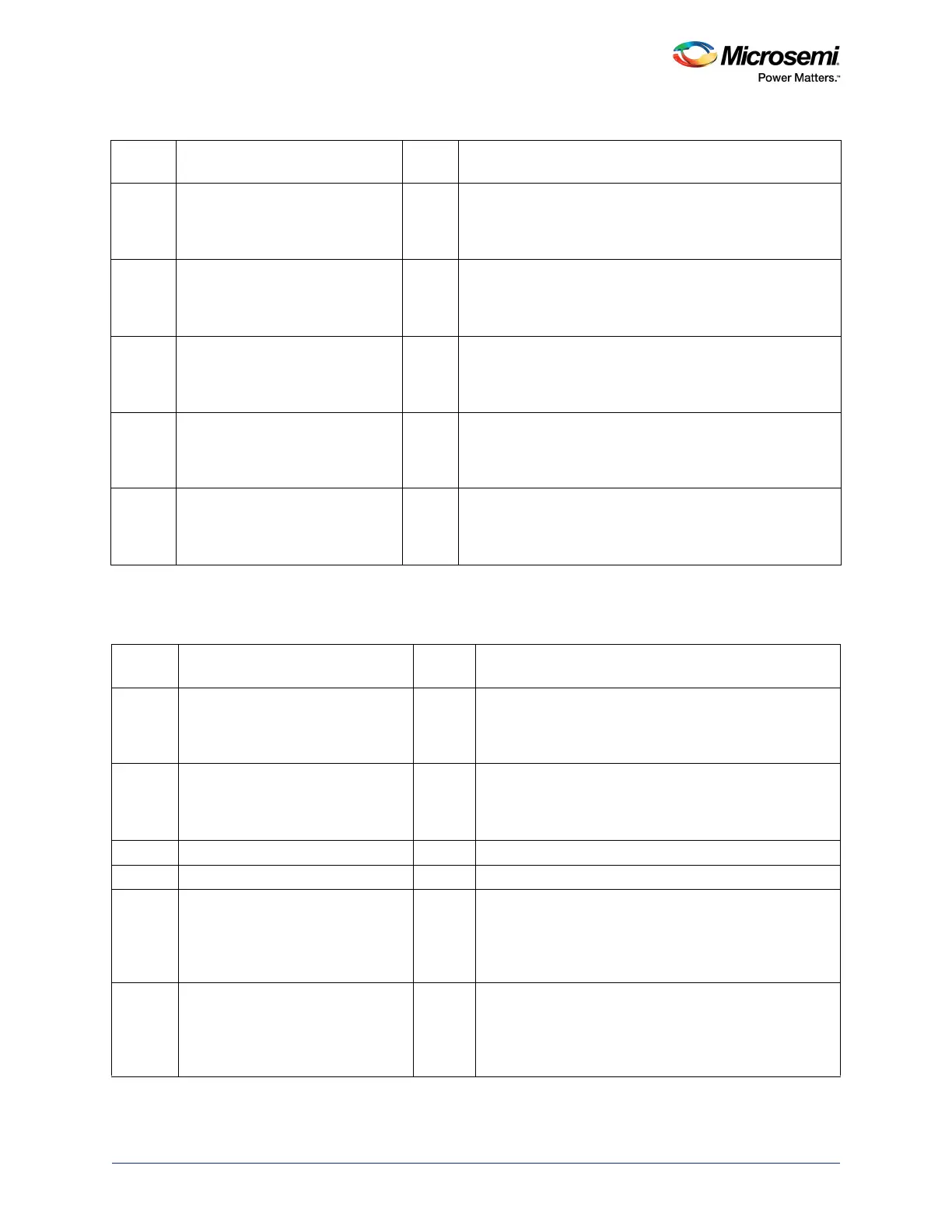

4 HPDMAICR_NON_WORD_INT[0] 0 When this bit is set, HPDMA clears the

HPDMAEDR_DCP_NON_WORD_ERR[0] bit in the Empty

Descriptor register.

These bits always read back as 0.

5 HPDMAICR_NON_WORD_INT[1] 0 When this bit is set, HPDMA clears the

HPDMAEDR_DCP_NON_WORD_ERR[1] bit in the Empty

Descriptor Register.

These bits always read back as 0.

6 HPDMAICR_NON_WORD_INT[2] 0 When this bit is set, HPDMA clears the

HPDMAEDR_DCP_NON_WORD_ERR[2] bit in the Empty

Descriptor register.

These bits always read back as 0.

7 HPDMAICR_NON_WORD_INT[3] 0 When this bit is set, HPDMA clears the

HPDMAEDR_DCP_NON_WORD_ERR[3] bit in the Empty

Descriptor register.

These bits always read back as 0.

31:8 Reserved 0 Software should not rely on the value of a reserved bit. To

provide compatibility with future products, the value of a

reserved bit should be preserved across a read-modify-write

operation.

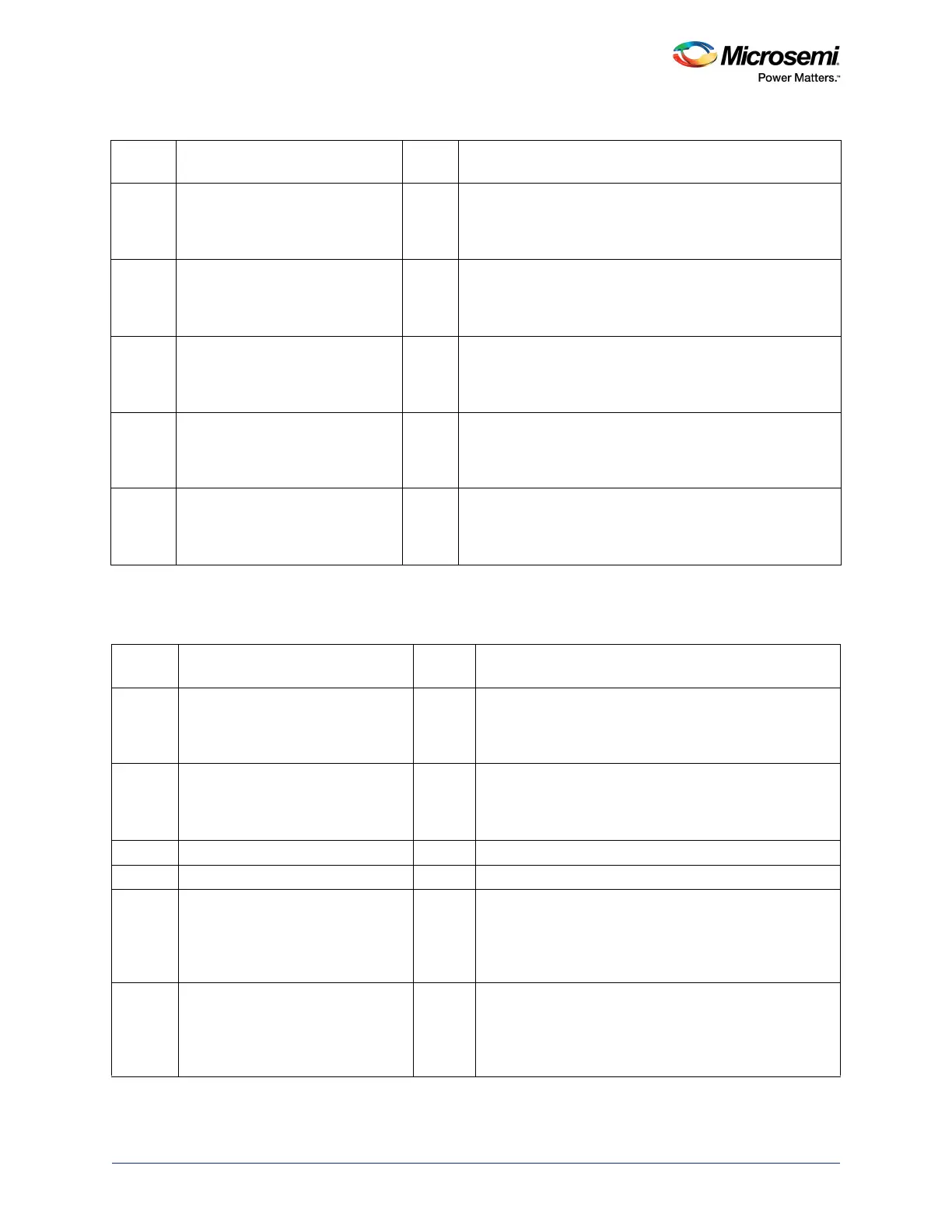

Table 172 • HPDMADR_REG

Bit

Number Name

Reset

Value Description

0 HPDMADR_BFR_EMPTY 1 Data buffer is empty; HPDMA controller initiates idle

transfers on the destination memory end.

1: Data buffer is empty.

0: Data Buffer is not empty.

1 HPDMADR_BFR_FULL 0 Data buffer is full; HPDMA controller initiates idle transfers

on the source memory end.

1: Data buffer is full.

0: Data buffer is not full.

4:2 HPDMADR_BFR_RD_PNTR[2:0] 0 HPDMA data buffer read pointer

7:5 HPDMADR_BFR_WR_PNTR[2:0] 0 HPDMA data buffer write pointer

11:8 HPDMADR_AHM1_CST_DBG[3:0] 0 Master 1 (AHB bus matrix) current state

0001 – IDLE

0010 – WRITE

0100 – READ

1000 – WAIT

15:12 HPDMADR_AHM2_CST_DBG[3:0] 0 Master 2 (MSS DDR bridge) current state

0001 – IDLE

0010 – WRITE

0100 – READ

1000 – WAIT

Table 171 • HPDMAICR_REG (continued)

Bit

Number Name

Reset

Value Description

Loading...

Loading...