System Register Block

UG0331 User Guide Revision 15.0 695

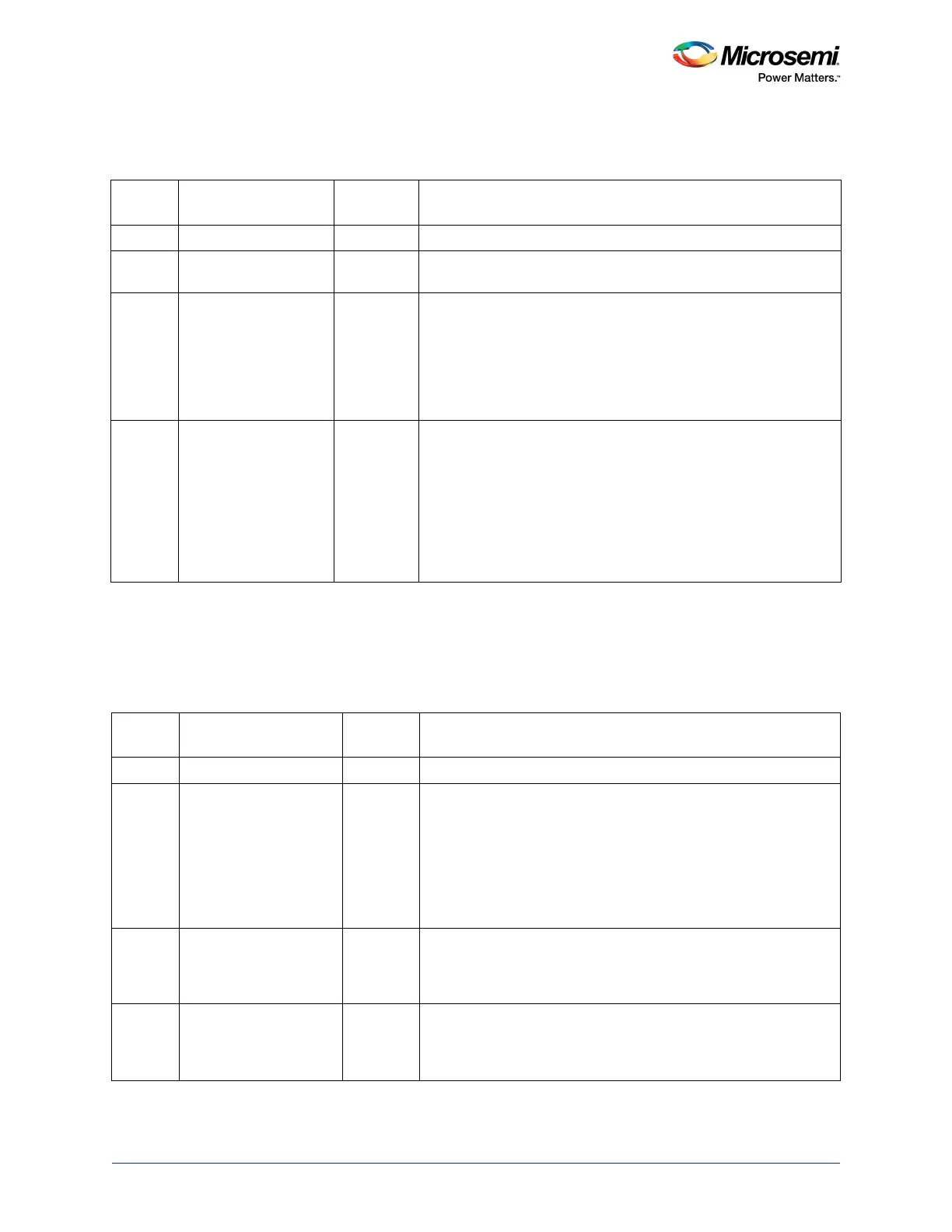

22.3.21 M3 Configuration Register

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

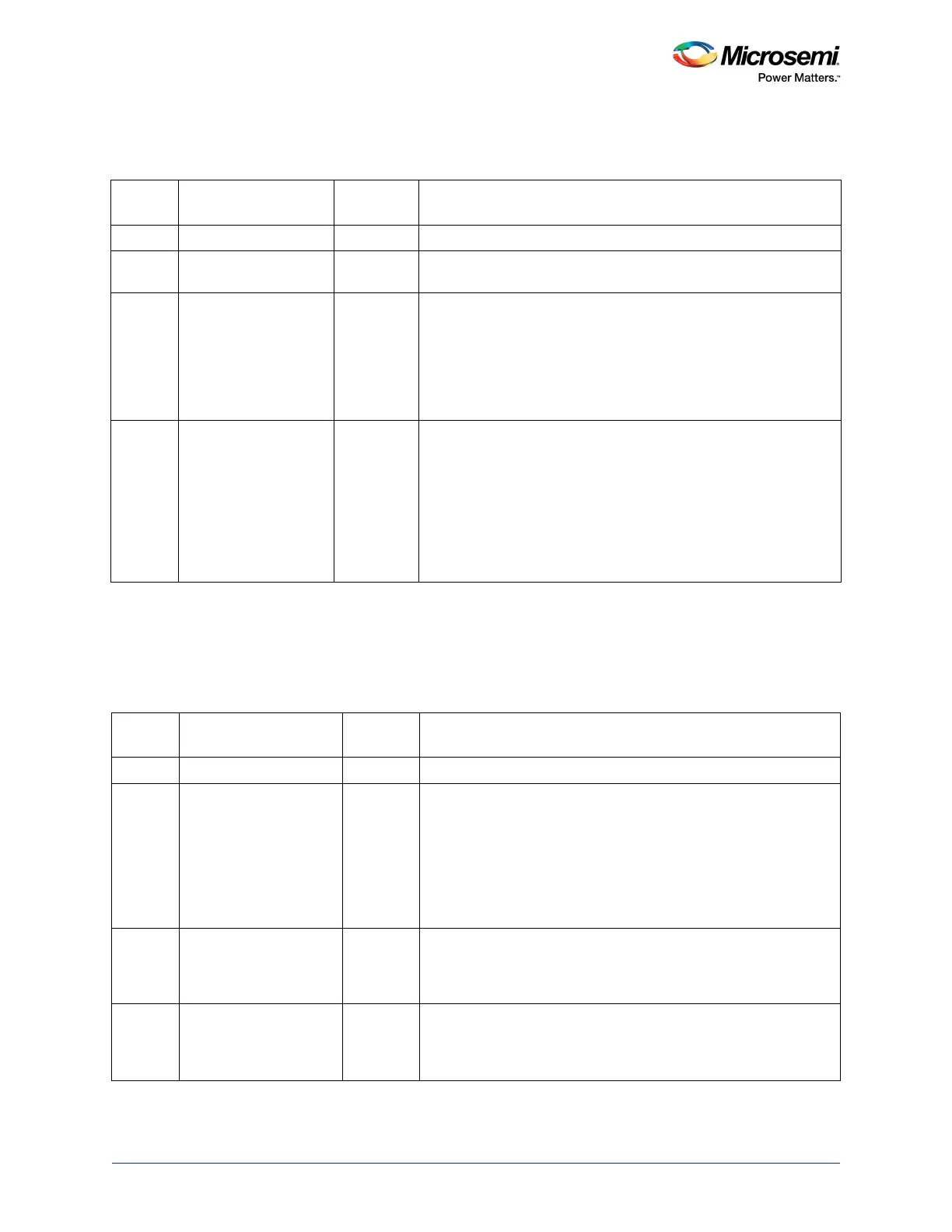

22.3.22 Fabric Interface Control (FIC) Register

Table 675 • M3_CR

Bit

Number Name Reset Value Description

[31:29] Reserved 0

28 M3_MPU_DISABLE 0 When set, disables the memory protection unit (MPU) within the

Cortex-M3 processor.

[27:26] STCLK_DIVISOR 0x3 Configures the amount of division to be performed on M3_CLK, in

order to generate the STCLK input for the Cortex-M3 processor.

This is used to control the frequency of STCLK.

00: M3_CLK/4

01: M3_CLK/8

10: M3_CLK/16

11: M3_CLK/32

[25:0] STCALIB[25:0] 0x2000000 Used as the STCALIB input for the Cortex-M3 processor. It

determines the rollover value for the internal SysTick timer of the

Cortex-M3 processor. The bit definitions for this field are as follows:

STCALIB[25] – NOREF bit of SysTick Calibration Value Register; 1

indicates STCLK is not provided.

STCALIB[24] – SKEW bit of SysTick Calibration Value Register; 1

indicates calibration value is not exactly 10 ms.

STCALIB[23:0] – TENMS field of SysTick Calibration Value

Register; reload value to use for 10 ms timing.

Table 676 • FAB_IF_CR

Bit

Number Name

Reset

Value Description

[31:10] Reserved 0

[9:4] SW_FIC_REG_SEL 0x38 Indicates whether a specific fabric region is accessible by FIC_0 or

FIC_1. This register should not be changed during operation.

0: Fabric region associated with FIC_0

1: Fabric region associated with FIC_1

By default, fabric region 0, 1, 2 are accessible through FIC_0 and

regions 3, 4, 5 are accessible through FIC_1.

These bits are driven into the AHB bus in order to allocate a

specific memory region to either FIC_0 or FIC_1.

3 FAB1_AHB_MODE 0 Controls whether the FIC_1 fabric interface supports AHB mode or

APB mode. Allowed values:

0: Supports APB mode

1: Supports AHB mode

2 FAB0_AHB_MODE 0 Controls whether FIC_0 fabric interface supports AHB mode or

APB mode. Allowed values:

0: Supports APB mode

1: Supports AHB mode

Loading...

Loading...