Ethernet MAC

UG0331 User Guide Revision 15.0 375

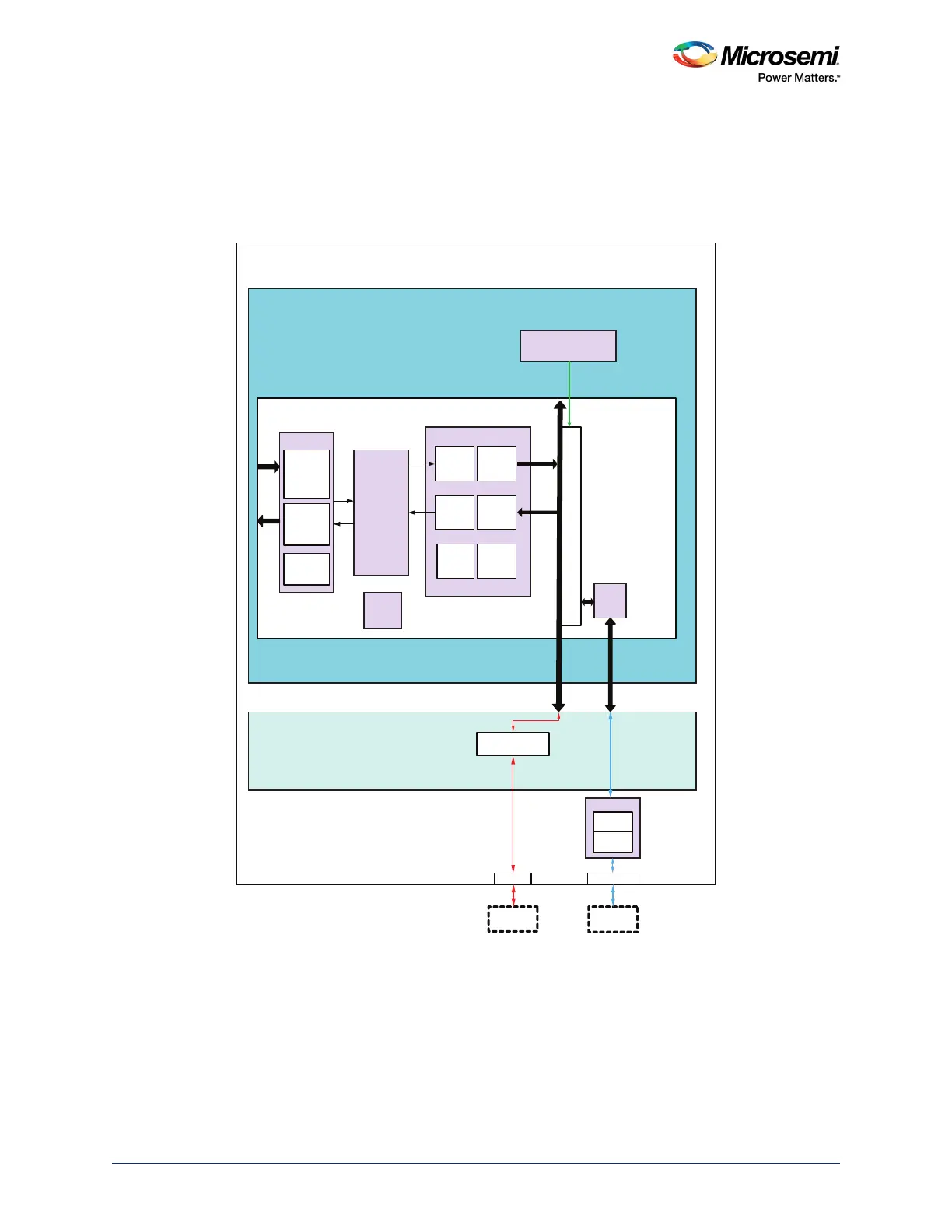

11.2 Functional Description

The TSEMAC controller is interfaced through the advanced high-performance bus (AHB) matrix in the

MSS. SmartFusion2 TSEMAC provides three interfaces (MII, GMII, and TBI) to connect to the external

PHY. The following figure shows the block diagram for the connections between the EMAC and FPGA

fabric.

Figure 153 • TSEMAC Block Diagram

11.2.1 EMAC Functional Blocks

EMAC has five functional sub-blocks:

• AHB Engine

• MAC TX and RX FIFO

• PE-MCXMAC

• MAC Statistics Module

• SGMII Module

Ethernet MAC

AHBEngine

DMA controller

+

AHB Master

interface port

DMA

controller

+

AHB Slave

interface port

AHB

Decoder

MAC TX

& RX

FIFOs

PE _MCXMAC

PETMC

Tx MAC

Control

PERMC

Rx MAC

Control

PEHST

Host

Interface

PETFN

Transm it

function

PERFN

Receive

function

PEMGT

MII

Management

interface

MUX - DeMUX

SGMII

MAC

Statistics

Collector

FABRIC

SERDES I/O’s

SGMII

PHY

System Registers

MSS

TBI

GMII /MII

GMII/MII

10/100/1000 Mbps

MSIO

GMII/MII

PHY

SmartFusion2

EPCS

SERDES

SERDESIF0/1

Loading...

Loading...