Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 115

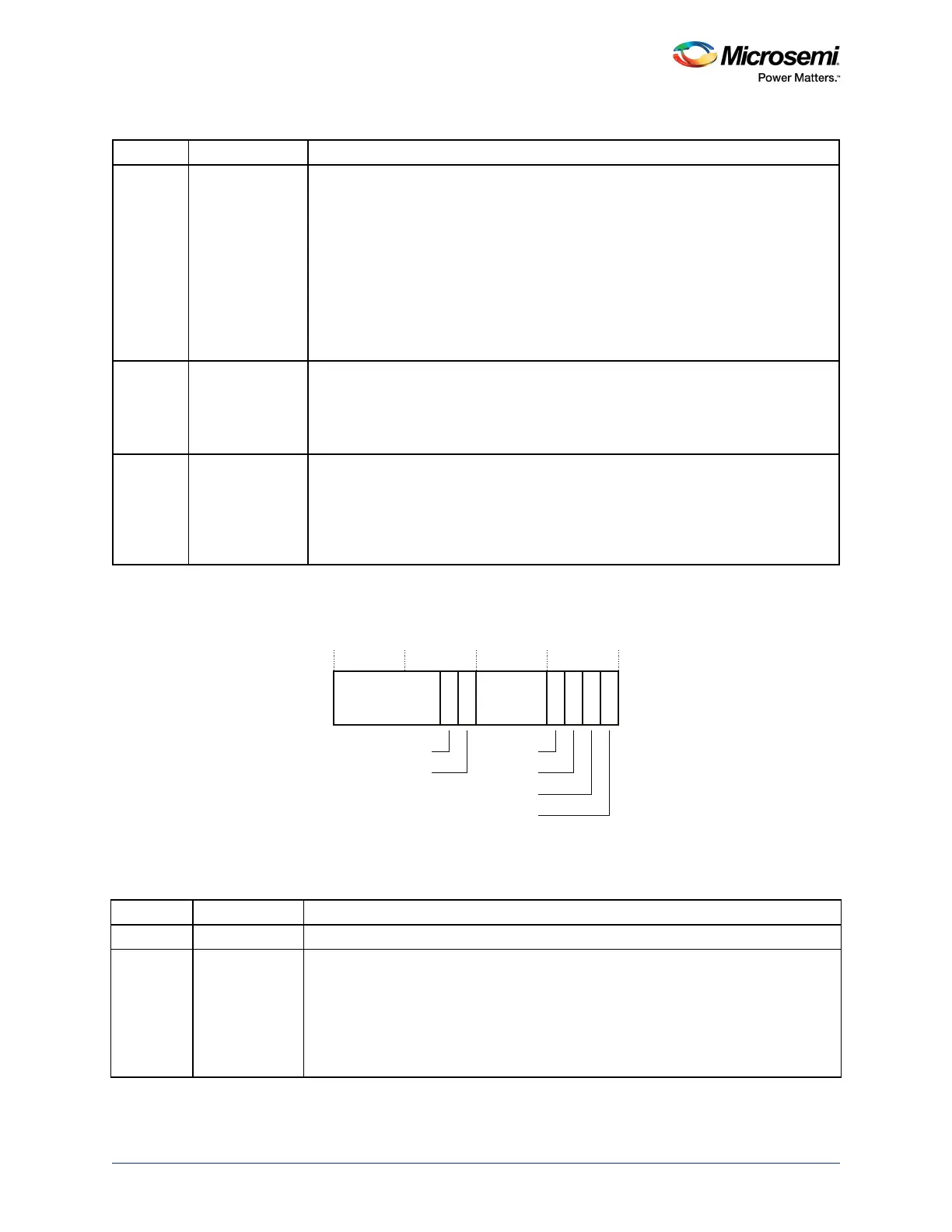

3.7.2.13 UsageFault Status Register

The UFSR indicates the cause of a UsageFault. The bit assignments are:

Figure 44 • UFSR Bit Assignments

[2] IMPRECISERR Imprecise data bus error:

0: no imprecise data bus error

1: a data bus error has occurred, but the return address in the stack frame is not

related to the instruction that caused the error.

When the processor sets this bit to 1, it does not write a fault address to the BFAR.

This is an asynchronous fault. Therefore, if it is detected when the priority of the

current process is higher than the BusFault priority, the BusFault becomes pending

and becomes active only when the processor returns from all higher priority

processes. If a precise fault occurs before the processor enters the handler for the

imprecise BusFault, the handler detects both IMPRECISERR set to 1 and one of the

precise fault status bits set to 1.

[1] PRECISERR Precise data bus error:

0: no precise data bus error

1: a data bus error has occurred, and the PC value stacked for the exception return

points to the instruction that caused the fault.

When the processor sets this bit is 1, it writes the faulting address to the BFAR.

[0] IBUSERR Instruction bus error:

0: no instruction bus error

1: instruction bus error.

The processor detects the instruction bus error on prefetching an instruction, but it

sets the IBUSERR flag to 1 only if it attempts to issue the faulting instruction.

When the processor sets this bit is 1, it does not write a fault address to the BFAR.

Table 66 • UFSR Bit Assignments

Bits Name Function

[15:10] Reserved.

[9] DIVBYZERO Divide by zero UsageFault:

0: no divide by zero fault, or divide by zero trapping not enabled

1: the processor has executed an

SDIV

or

UDIV

instruction with a divisor of 0.

When the processor sets this bit to 1, the PC value stacked for the exception return

points to the instruction that performed the divide by zero.

Enable trapping of divide by zero by setting the DIV_0_TRP bit in the CCR to 1, see

Configuration and Control Register, page 109.

Table 65 • BFSR Bit Assignments (continued)

Bits Name Function

NOCP

INVPC

INVSTATE

UNDEFINSTR

DIVBYZERO

UNALIGNED

15 10 9 8 7 4 3 2 1 0

Reserved Reserved

Loading...

Loading...