System Register Block

UG0331 User Guide Revision 15.0 709

22.3.40 PLL LOCK Enable Control Register

22.3.41

MSS DDR Clock Calibration Control Register

22.3.42 PLL Delay Line Select Control Register

[1:0] RTC_CLK_SEL 0 Indicates which of the possible clocks are to be configured as the

source of the MSS RTC clock. The allowed values are as follows:

00: RTC_CLK comes from XTLOSC_CLK

01: RTC_CLK comes from RCOSC_1MHZ.

10: RTC_CLK comes from RCOSC_25_50MHZ

11: RTC_CLK comes from RTC_XTLOSC_CLK

The reset signal for this bit is SYSRESET_N.

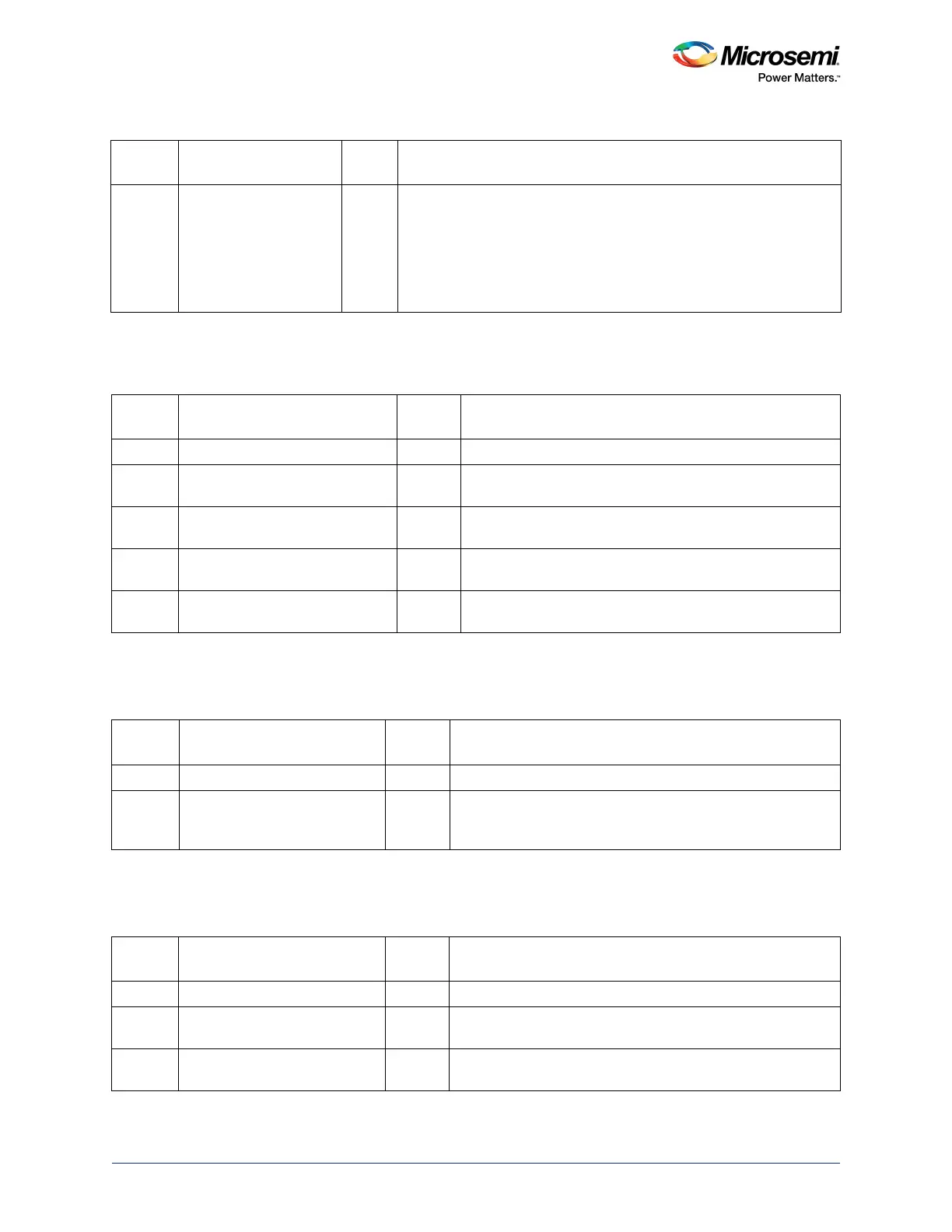

Table 697 • PLL_LOCK_EN_CR

Bit

Number Name

Reset

Value Description

[31:4] Reserved 0

3 FAB_PLL_LOCK_LOST_EN 0 Masking signal to enable Fabric PLL LOCK LOST interrupt

to Cortex-M3 processor.

2 FAB_PLL_LOCK_EN 0 Masking signal to enable Fabric PLL LOCK interrupt to

Cortex-M3 processor.

1 MPLL_LOCK_LOST_EN 0 Masking signal to enable MPLL LOCK LOST interrupt to

Cortex-M3 processor.

0 MPLL_LOCK_EN 0 Masking signal to enable MPLL LOCK interrupt to Cortex-M3

processor.

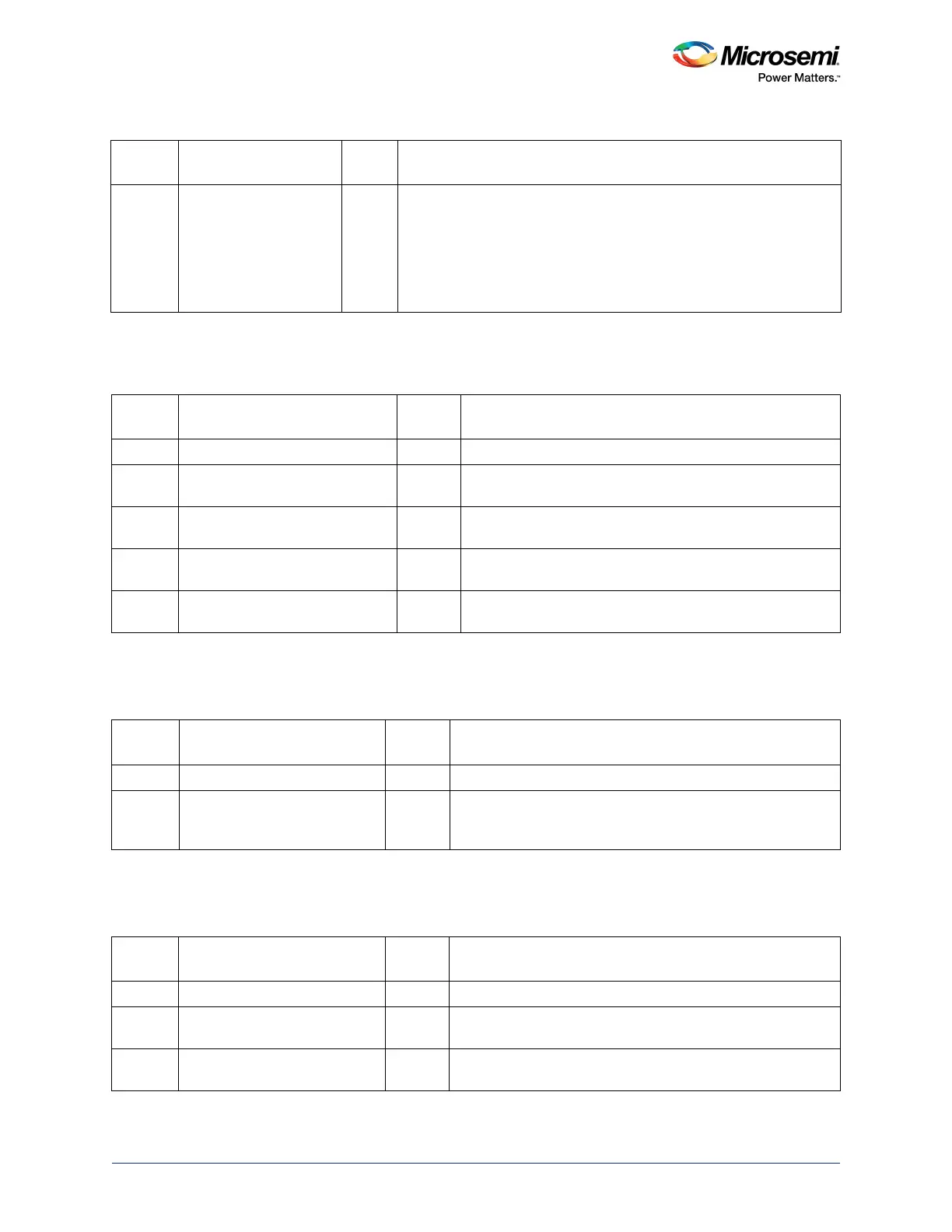

Table 698 • MSSDDR_CLK_CALIB_CR

Bit

Number Name

Reset

Value Description

[31:1] Reserved 0

0 FAB_CALIB_START 0 Writing to this bit causes a one clock tick pulse to be

generated on FABCALIBSTART. This is used to start an FPGA

fabric calibration test circuit.

Table 699 • PLL_DELAY_LINE_SEL_CR

Bit

Number Name

Reset

Value Description

[31:4] Reserved 0

3:2 PLL_FB_DEL_SEL 0 Must be programmed to a specific value by Libero SoC and

never be modified after that.

1:0 PLL_REF_DEL_SEL 0 Must be programmed to a specific value by Libero SoC and

never be modified after that.

Table 696 • MSSDDR_FACC2_CR (continued)

Bit

Number Name

Reset

Value Description

Loading...

Loading...