Ethernet MAC

UG0331 User Guide Revision 15.0 393

11.7 EMAC Configuration Register Summary

Each descriptor comprises a sequence of three 32-bit memory locations as shown in Table 323,

page 381.

The following table summarizes each of the registers covered in this document. The EMAC base address

is 0x40041000.

.

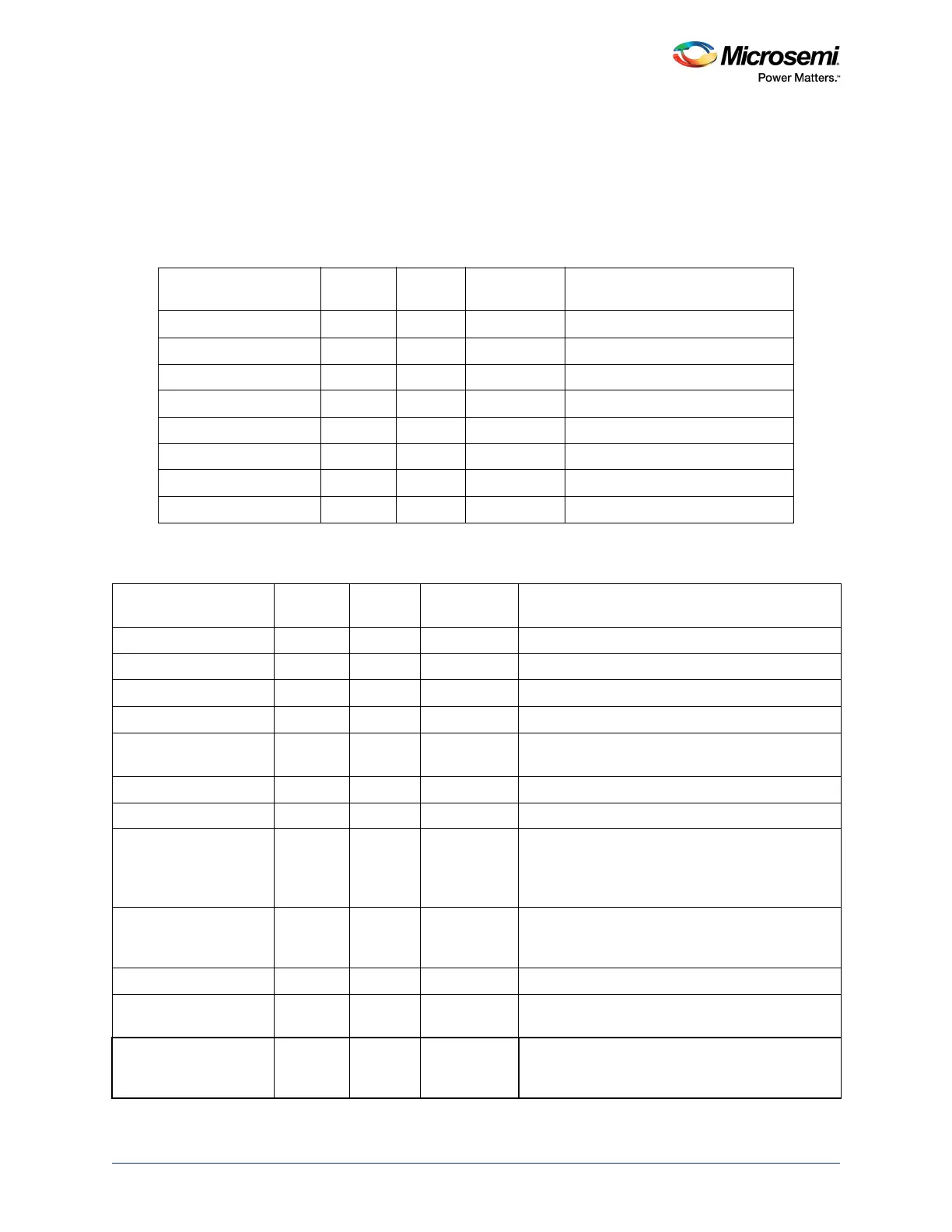

Table 332 • EMAC M-AHB Register Map

Register Name

Address

Offset

Register

Type Reset Value Description

DMA_TX_CTRL 0x180 R/W 0x0 Transmit control register

DMA_TX_DESC 0x184 R/W 0x0 Pointer to transmit descriptor

DMA_TX_STATUS 0x188 R/W 0x0 Transmit status register

DMA_RX_CTRL 0x18C R/W 0x0 Receive control register

DMA_RX_DESC 0x190 R/W 0x0 Pointer to receive descriptor

DMA_RX_STATUS 0x194 R/W 0x0 Receive status register

DMA_IRQ_MASK 0x198 R/W 0x0 Interrupt mask register

DMA_IRQ 0x19C RO 0x0 Interrupts register

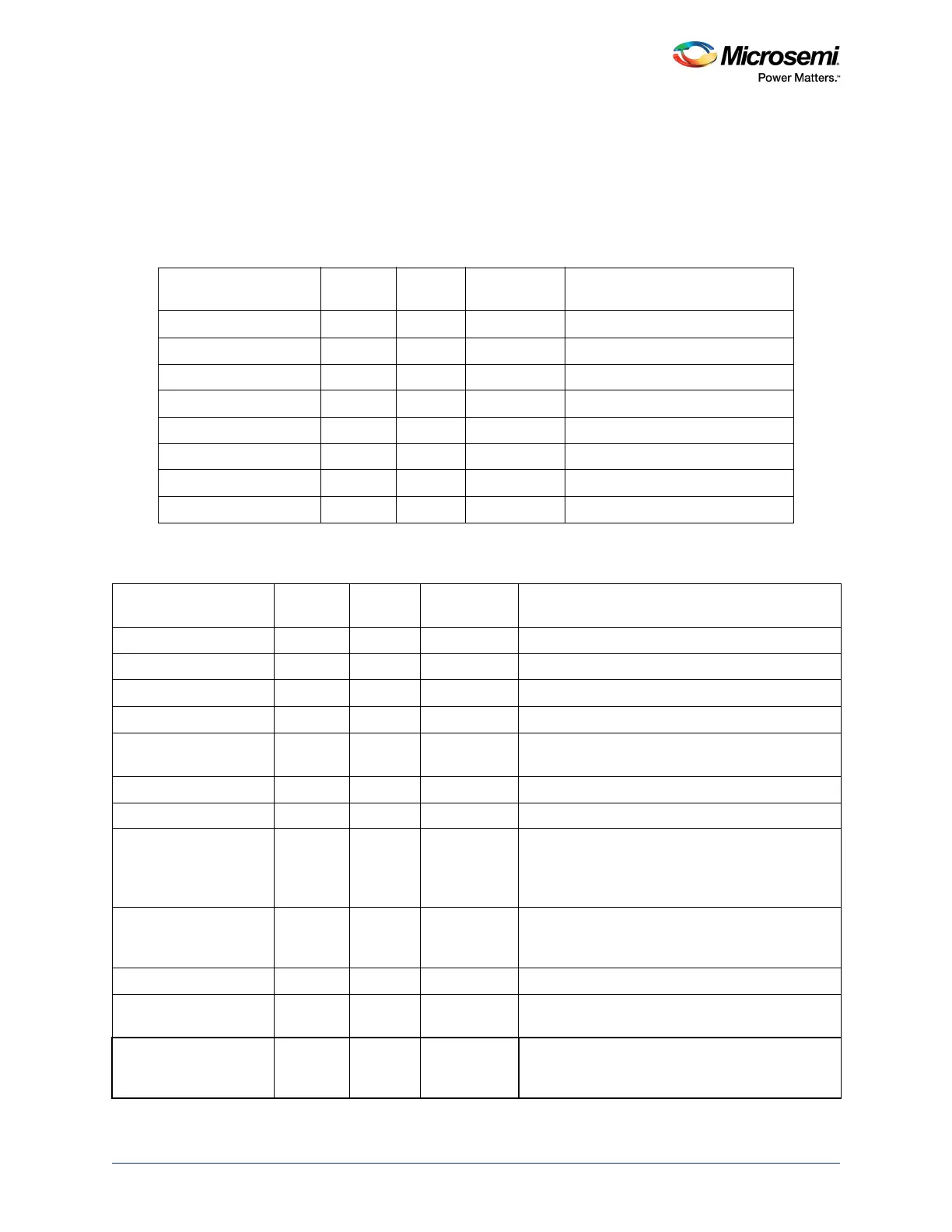

Table 333 • EMAC PE-MCXMAC Register Map

Register Name

Address

Offset

Register

Type Reset Value Description

CFG1 0x00 R/W 0x80000000 MAC configuration register

CFG2 0x04 R/W 0x00007000 MAC configuration register

IFG 0x08 R/W 0x40605060 Inter packet gap and interframe gap register

HALF_DUPLEX 0x0C R/W 0x00A1F037 Definition of half duplex register

MAX_FRAME_LENGTH 0x10 R/W 0x00000600 Sets the maximum frame size in both transmit and

receive directions.

Reserved 0x14 R/W 0x0 Reserved

Reserved 0x18 R/W 0x0 Reserved

TEST 0x1C R/W 0x0 This test bit is used to predict back off times in

Half-duplex mode.

This allows the MAC to be paused for testing

purpose only.

MII_CONFIG 0x20 R/W 0x0 This resets MII MGMT, determines MGMT Clock

frequency and causes the MII MGMT to suppress

preamble generation.

MII_COMMAND 0x24 R/W 0x0 MONITORS link fails.

MII_ADDRESS 0x28 R/W 0x0 This represents 5-bit PHY address field and 5 bit

register address field.

MII_CTRL 0x2C WO 0x0 Control register for MII management write cycle

using the 16-bit data and the pre-configured PHY

and register addresses.

Loading...

Loading...