Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 315

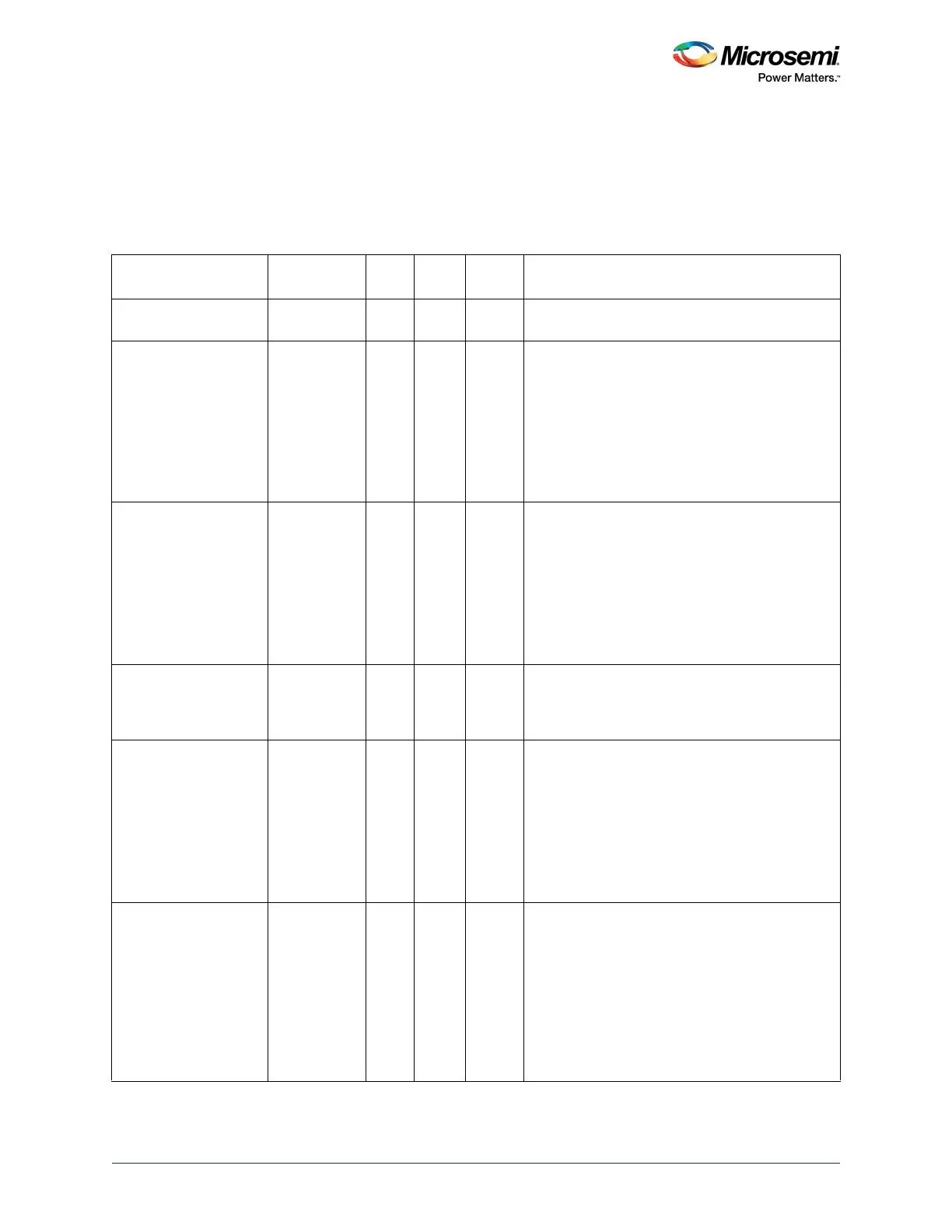

10.3.6 Indexed Registers

This section covers all the registers in this category along with the address offset, functionality, and per-

bit details. The registers mapped into this section depend on whether the core is in Peripheral mode

(DEV_CTRL_REG.Bit2 = 0) or in Host mode (DEV_CTRL_REG.Bit2 = 1) and the value of the Index

register (INDEX_REG).

Table 211 • Indexed Register Set Description

Register Name Address Width

R/W

Type

Reset

Value Description

TX_MAX_P_REG 0x40043010 16 RW 0 Maximum packet size of host transmit endpoint.

(Index register set to select endpoints 1 – 4 only).

CSR0L_REG

(Peripheral)

CSR0L_REG (Host)

TX_CSRL_REG

(Peripheral)

TX_CSRL_REG (Host)

0x40043012 8 RW 0 Provide control and status bits for endpoint0

(Index register set to select endpoint0) and

transmit endpoint0 (Index register set to select

endpoints 1 – 4).

The interpretation of the register depends on

whether the USB controller is acting as a

peripheral or a host. The value returned when the

register is read reflects the status attained; for

example, as a result of writing to the register.

CSR0H_REG

(Peripheral)

CSR0H_REG (Host)

TX_CSRH_REG

(Peripheral)

TX_CSRH_REG (Host)

0x40043013 8 RW 0 Provides control and status bits for endpoint0

(Index register set to select endpoint0) and

transmit endpoint0 (Index register set to select

endpoints 1 – 4).

The interpretation of the register depends on

whether the USB controller is acting as a

peripheral or a host. The value returned when the

register is read reflects the status attained; for

example, as a result of writing to the register.

RX_MAX_P_REG 0x40043014 16 RW 0 Defines the maximum amount of data that can be

transferred through the selected receive endpoint

in a single operation. There is one such register

for each receive endpoint (except endpoint 0).

RX_CSRL_REG

(Peripheral)

RX_CSRL_REG (Host)

0x40043016 8 RW 0 Provide control and status bits for transfers

through the currently selected receive endpoint.

There is one such register for each configured

receive endpoint (not including endpoint 0).

The interpretation of the register depends on

whether the USB controller is acting as a

peripheral or a host. The value returned when the

register is read reflects the status attained; for

example, as a result of writing to the register.

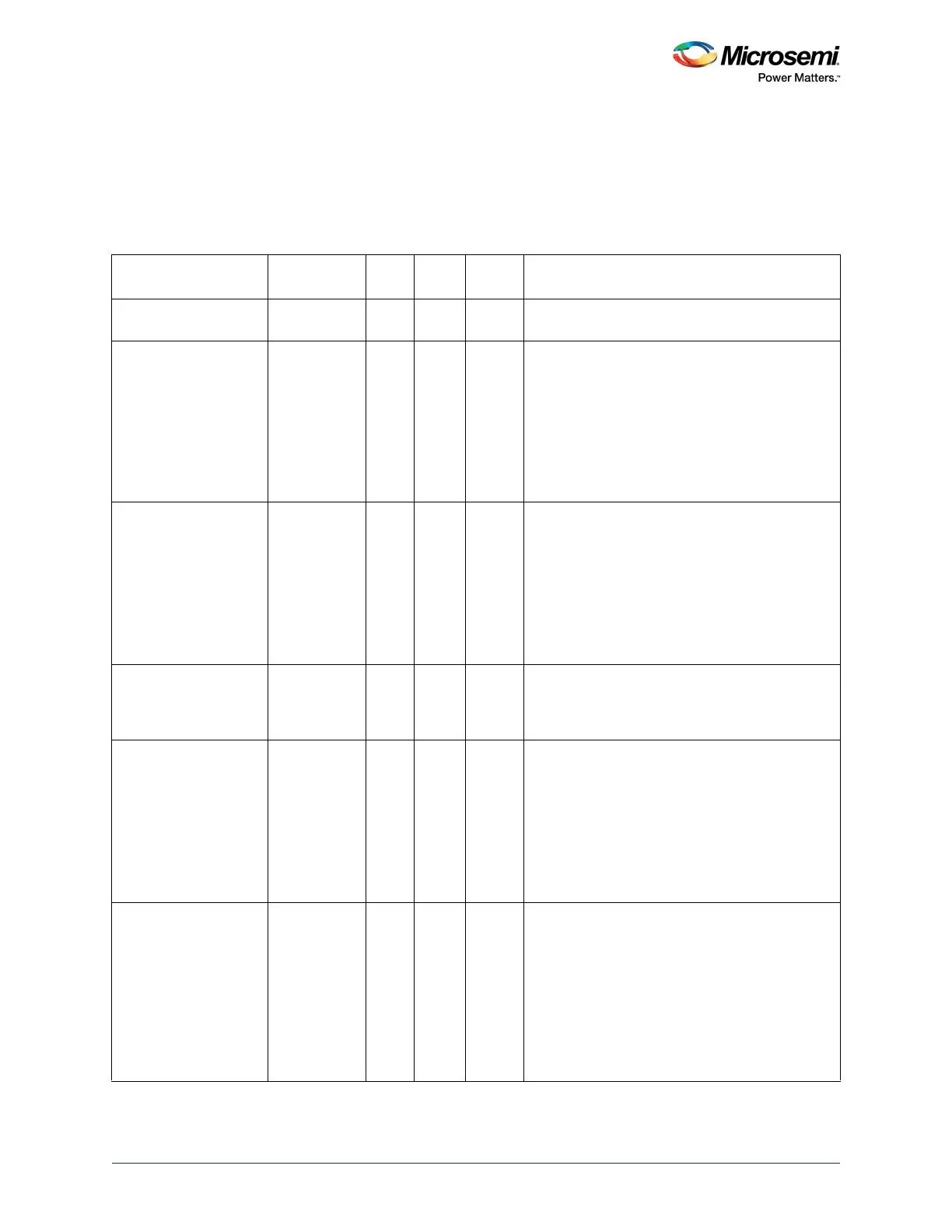

RX_CSRH_REG

(Peripheral)

RX_CSRH_REG (Host)

0x40043017 8 RW 0 Provides control and status bits for transfers

through the currently-selected receive endpoint

(Index register set to select endpoints 1 – 4 only).

There is one such register for each configured

receive endpoint (not including endpoint 0).

The interpretation of the register depends on

whether the USB controller is acting as a

peripheral or a host. The value returned when the

register is read reflects the status attained; for

example, as a result of writing to the register.

Loading...

Loading...