Ethernet MAC

UG0331 User Guide Revision 15.0 416

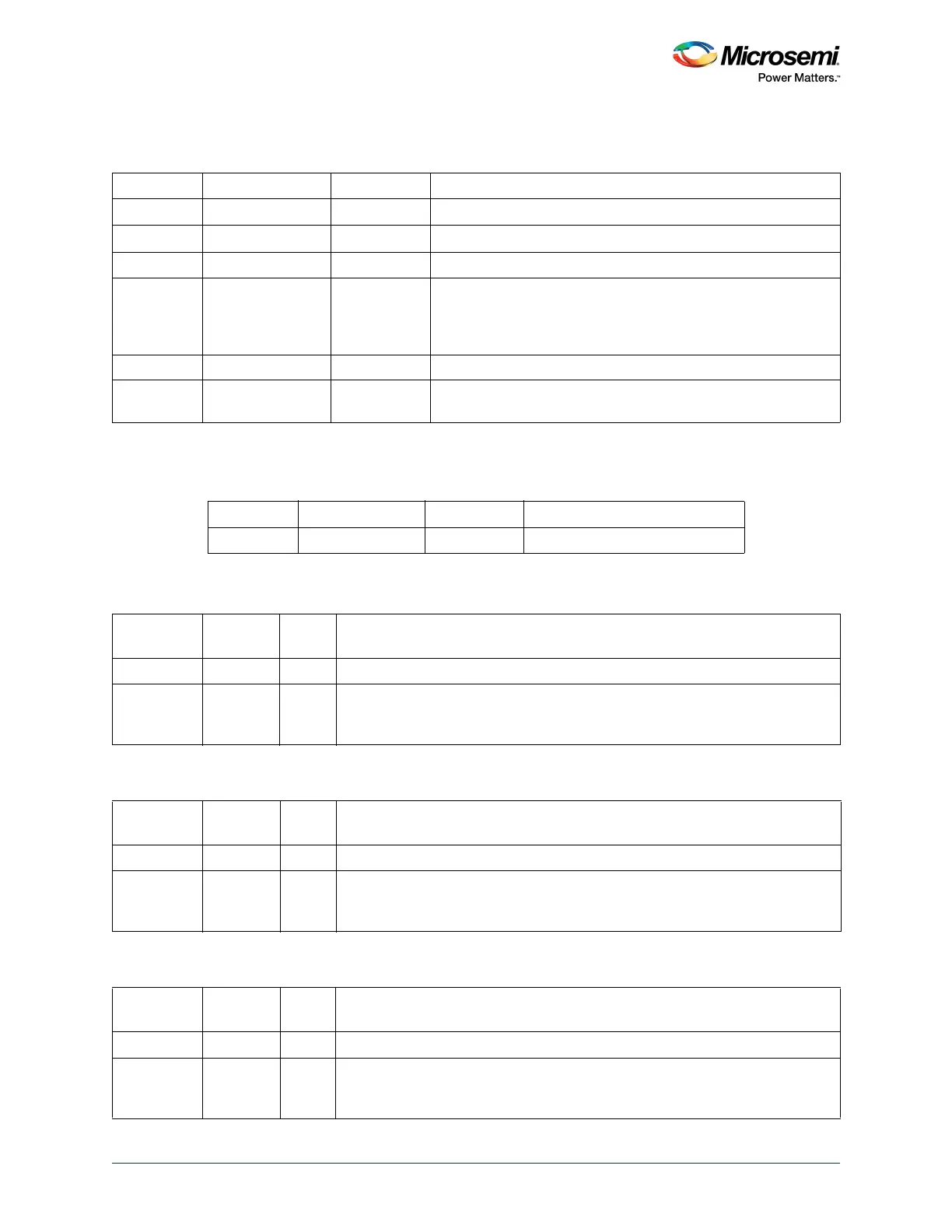

Table 375 • FIFO_RAM_ACCESS6

Bit Number Name Reset Value Description

31 hstrramrreq 0x0 Host receive RAM read request

30 hstrramrack 0x0 Host receive RAM read acknowledge

[29:24] Reserved 0x0 Reserved

[23:16] hstrramrdat

[39:32]

0x0 Host receive RAM read data

This is the upper byte of the receive FIFO RAM data that is read

at the address of the hstrramwadx[10:0] if the hstrramwadx[13] is

negated and the hstrramwreq is asserted.

[15:14] Reserved 0x0 Reserved

[13:0] hstrramradx

[13:0]

0x0 Host receive RAM read address

Table 376 • FIFO_RAM_ACCESS7

Bit Number Name Reset Value Description

[31:0] hstrramrdat 0x0 Host receive RAM read data

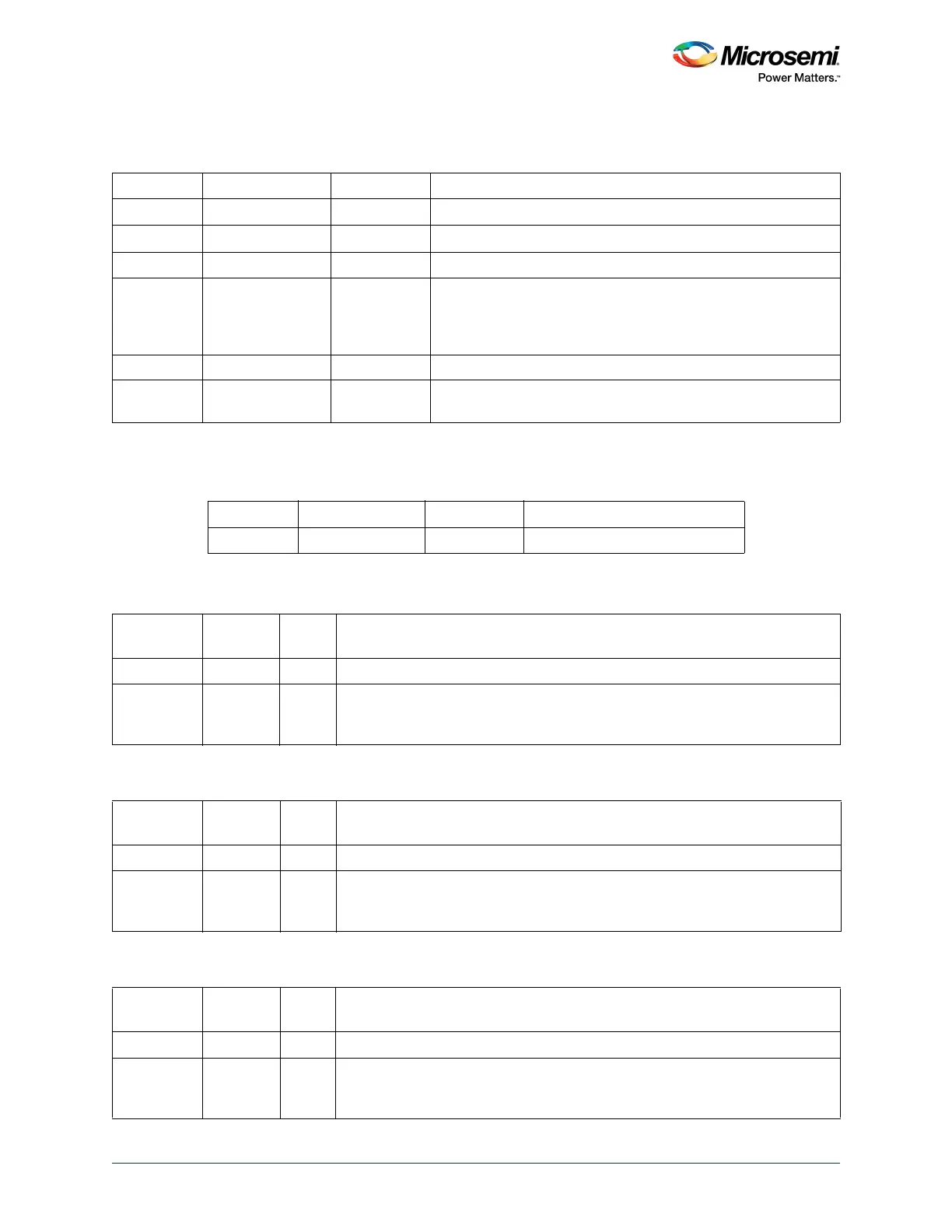

Table 377 • TR64

Bit Number Name

Reset

Value Description

[31:18] Reserved 0x0 Reserved

[17:0] TR64 0x0 Transmit and receive 64 byte frame counter: Incremented for each good or bad

transmitted and received frame, which is 64 bytes in length inclusive (excluding

framing bits but including FCS bytes).

Table 378 • TR127

Bit Number Name

Reset

Value Description

[31:18] Reserved 0x0 Reserved

[17:0] TR127 0x0 Transmit and receive 65 to 127 byte frame counter: Incremented for each good

or bad, transmitted and received frame, which is 65 to 127 bytes in length

inclusive (excluding framing bits but including FCS bytes).

Table 379 • TR255

Bit Number Name

Reset

Value Description

[31:18] Reserved 0x0 Reserved

[17:0] TR255 0x0 Transmit and receive 128 to 255 byte frame counter: Incremented for each good

or bad, transmitted and received frame, which is 128 to 255 bytes in length

inclusive (excluding framing bits but including FCS bytes).

Loading...

Loading...