Ethernet MAC

UG0331 User Guide Revision 15.0 403

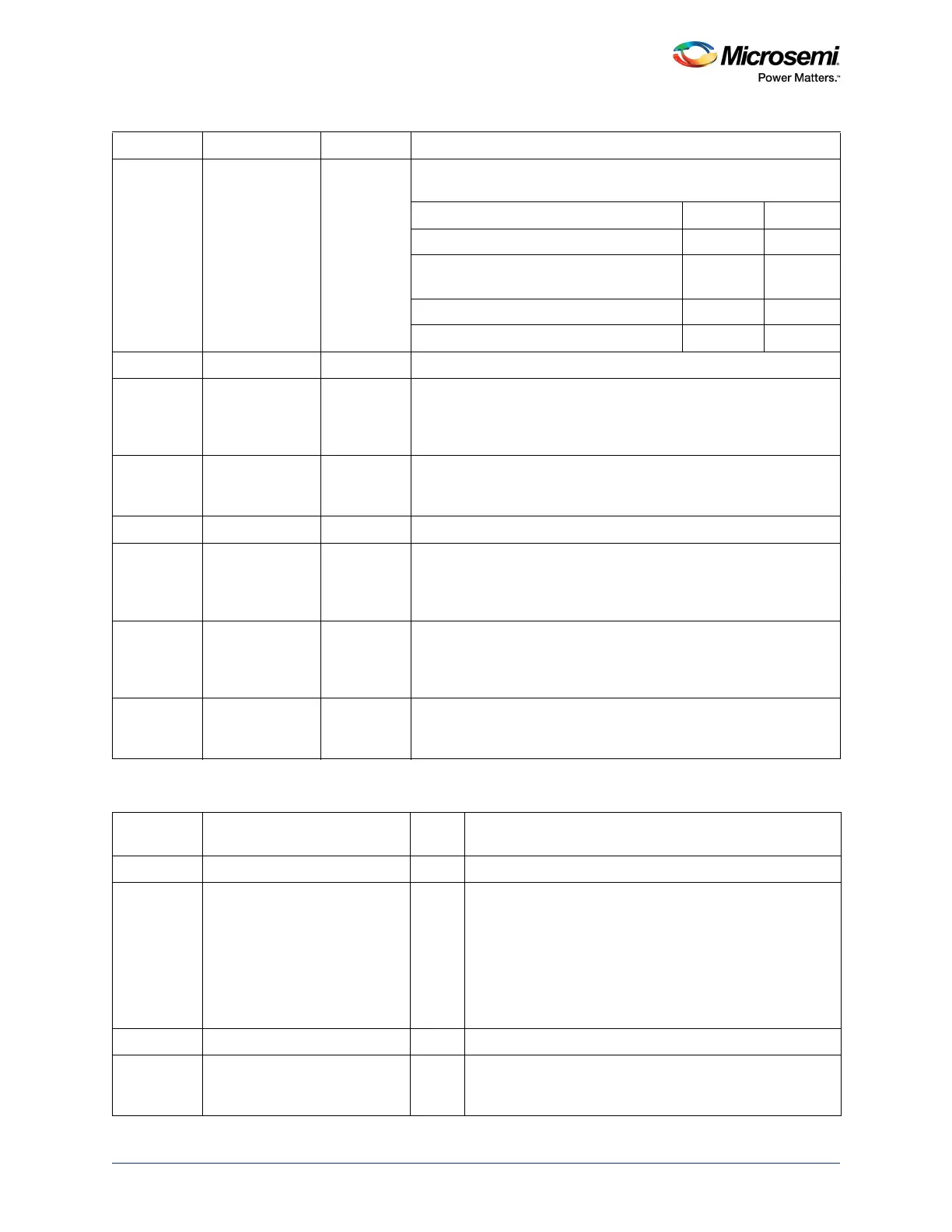

[9:8] INTERFACE

MODE

0x0 This field determines the type of interface the MAC is connected to.

The Interface mode settings are as follows.

Interface mode Bit 9 Bit 8

Reserved 0 0

Nibble mode (10/100 Mbps

MII/RMII/SMII, … )

01

Byte mode (1000 Mbps GMII/TBI) 1 0

Reserved 1 1

[7:6] Reserved 0x0 Reserved

5 HUGE FRAME

ENABLE

0x0 Set this bit to allow frames longer than the MAXIMUM FRAME

LENGTH to be transmitted and received. Clear this bit to have the

MAC limits the length of frames at the MAXIMUM FRAME LENGTH

value.

4 LENGTH FIELD

CHECKING

0x0 Set this bit to cause the MAC to check the frame’s length field to

ensure it matches the actual data field length. Clear this bit if no

length field checking is desired.

3 Reserved 0x0 Reserved

2 PAD/CRC

ENABLE

0x0 Set this bit to have the MAC pads all the short frames and appends

a CRC to every frame whether or not padding is required. Clear this

bit if frames, presented to the MAC, have a valid length and contain

a CRC.

1 CRC ENABLE 0x0 Set this bit to have the MAC appends a CRC to all the frames. Clear

this bit if frames, presented to the MAC, have a valid length and

contain a valid CRC. If the PAD/CRC ENABLE configuration bit or

the per-packet PAD/CRC ENABLE is set, CRC ENABLE is ignored.

0 FULL-DUPLEX 0x0 Setting this bit configures the PE-MCXMAC to operate in

Full-duplex mode. Clearing this bit configures the PE-MCXMAC to

operate in Half-duplex mode only.

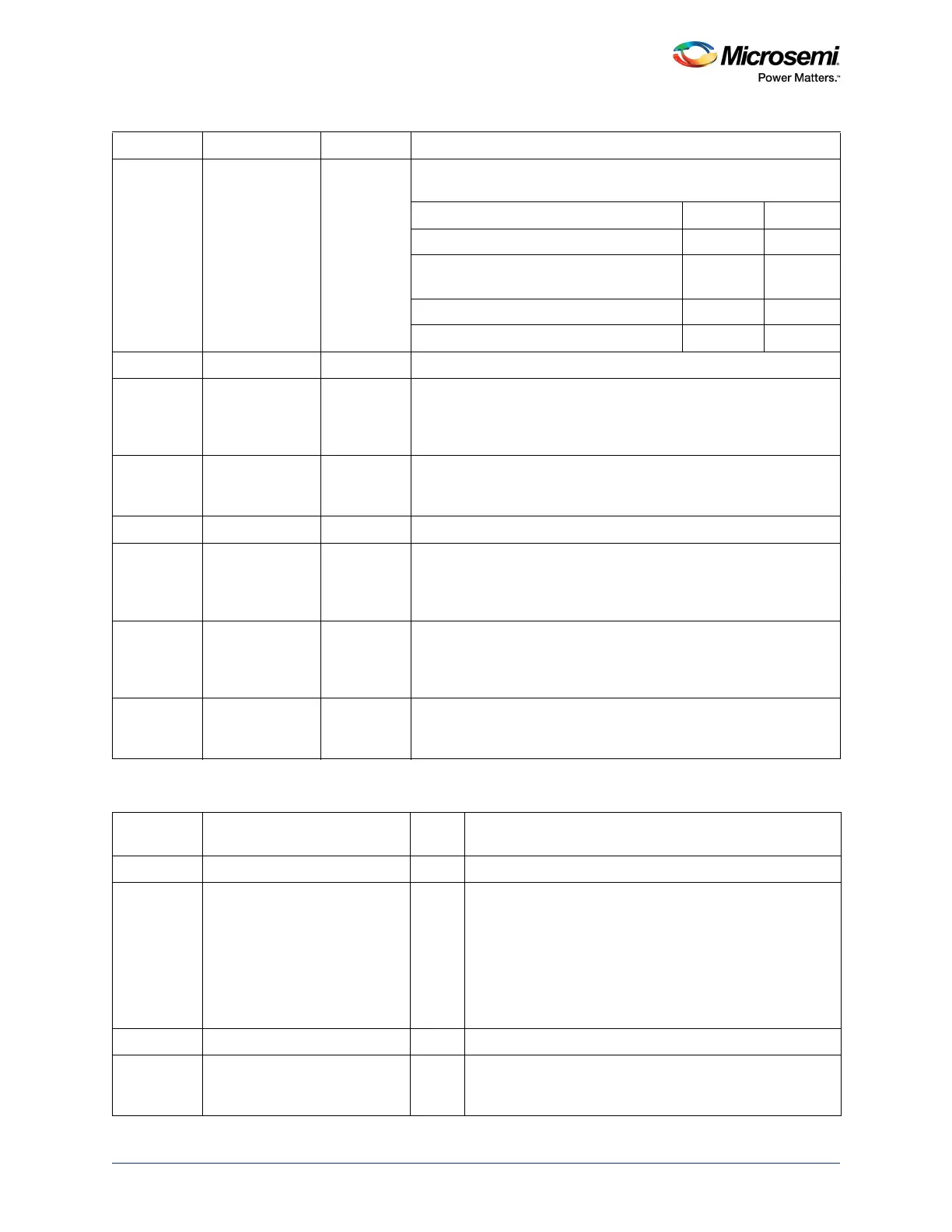

Table 349 • IFG

Bit Number Name

Reset

Value Description

31 Reserved 0x0 Reserved

[30:24] NON-BACK-TO-BACK INTER-

PACKET-GAP PART 1 (IPGR1)

0x40 This programmable field represents the optional carrier

Sense window, which is referenced in the IEEE

802.3/4.2.3.2.1 ‘Carrier Deference’. If a carrier is detected

during the timing of IPGR1, the MAC defers to the carrier.

However, the carrier becomes active after IPGR1; the MAC

continues timing IPGR2 and transmit, knowingly causing a

collision. This ensures fair access to the medium. The

permitted range of values is 0x0 to IPGR2. Default is 0x40.

23 Reserved 0x0 Reserved

[22:16] NON-BACK-TO-BACK INTER-

PACKET-GAP PART 2 (IPGR2)

0x60 This programmable field represents the Non-Back-to-Back

Inter-Packet-Gap in the bit times, which represent the

minimum inter packet gap (IPG) of 96 bits.

Table 348 • CFG2 (continued)

Bit Number Name Reset Value Description

Loading...

Loading...