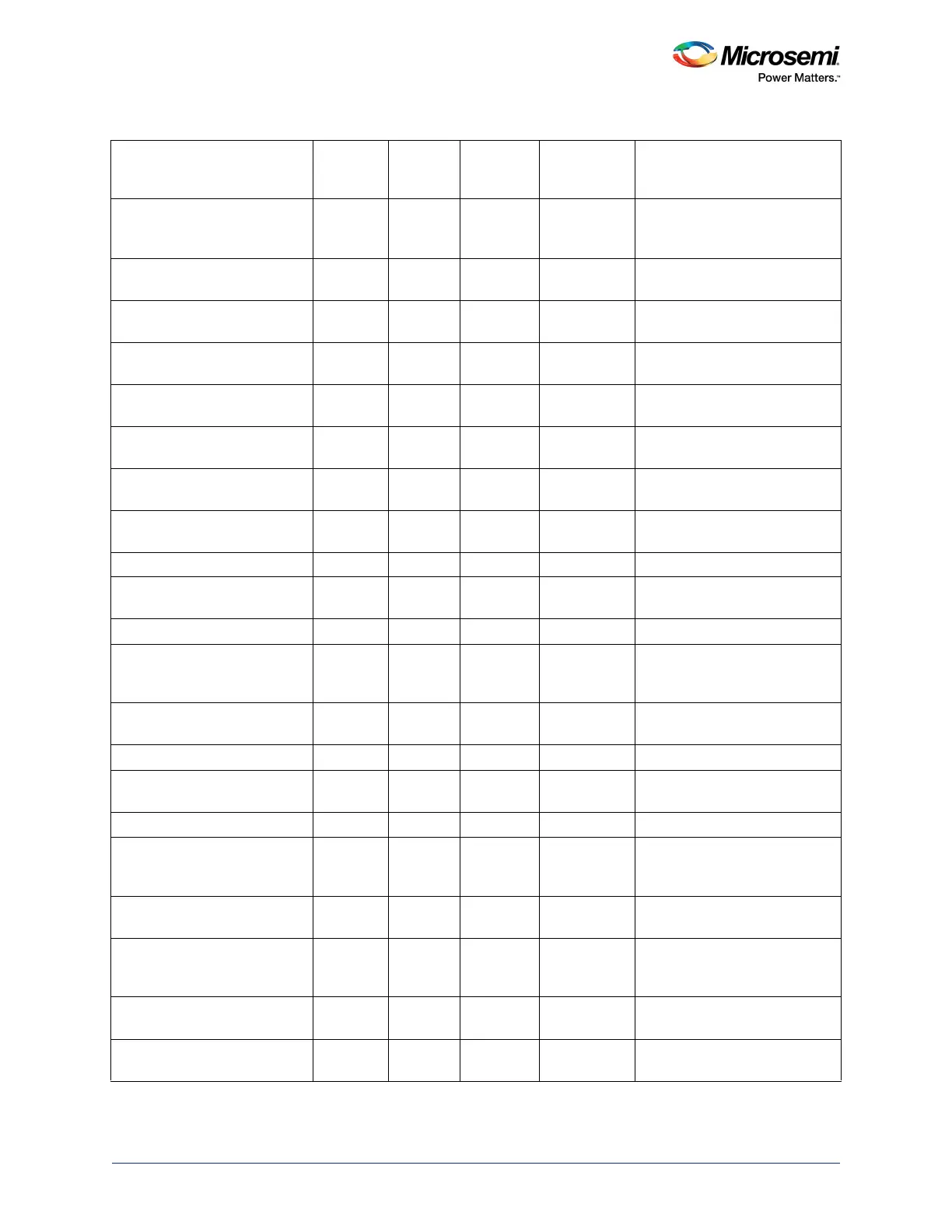

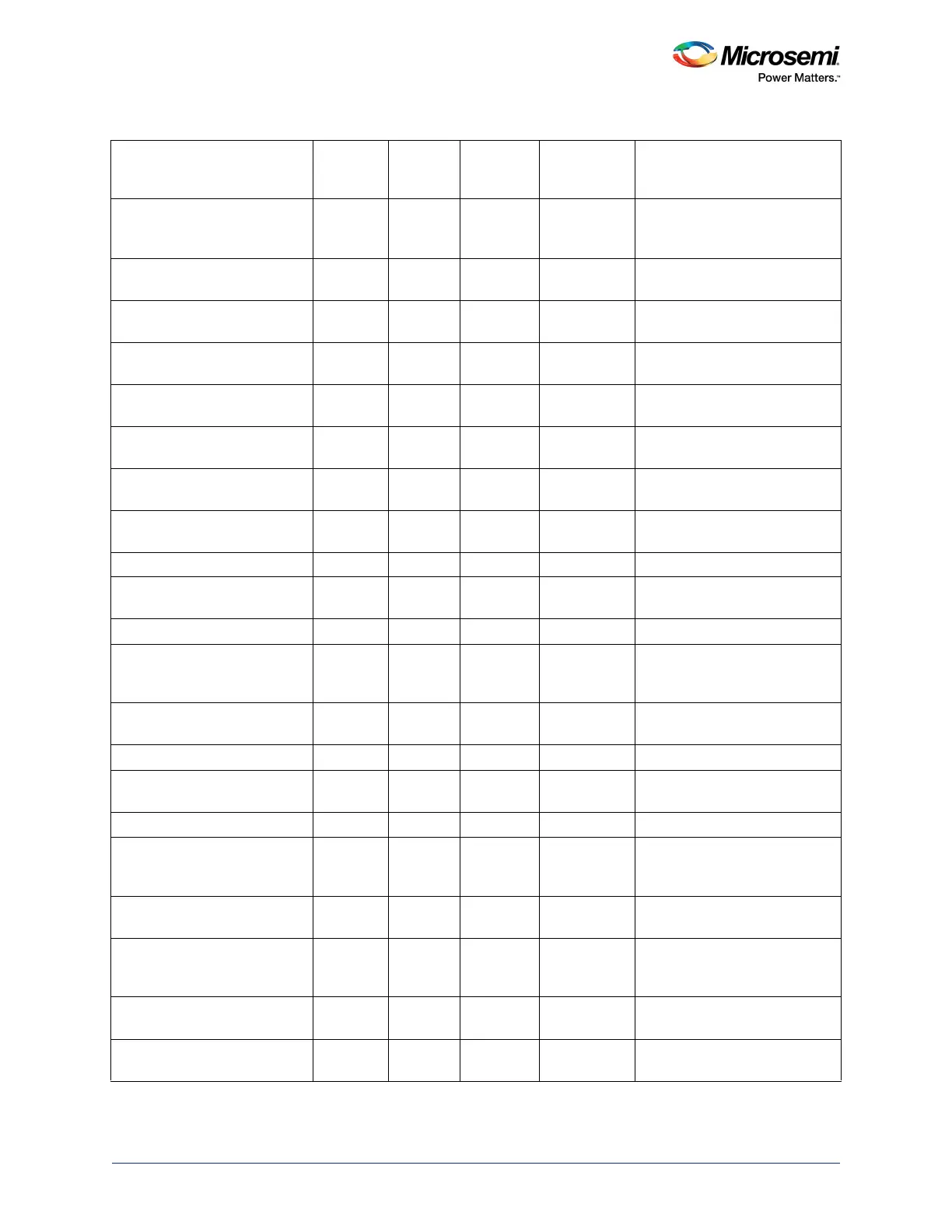

System Register Block

UG0331 User Guide Revision 15.0 677

EDAC_CR 0x38 RW-P Register SYSRESET_

N

EDAC Configuration Register

for eSRAM0, eSRAM1, USB,

MAC, and CAN

MASTER_WEIGHT0_CR 0x3C RW-P Register SYSRESET_

N

Master Weight Configuration

Register 0

MASTER_WEIGHT1_CR 0x40 RW-P Register SYSRESET_

N

Master Weight Configuration

Register 1

SOFT_IRQ_CR 0x44 RW-P Register SYSRESET_

N

Enables software interrupt

SOFT_RESET_CR 0x48 RW-P Bit SYSRESET_

N

Software Reset Control Register

M3_CR 0x4C RW-P Register SYSRESET_

N

Cortex M3 Configuration

Register

FAB_IF_CR 0x50 RW-P Register SYSRESET_

N

Controls fabric interface

LOOPBACK_CR 0x54 RW-P Register SYSRESET_

N

Controls MSS peripherals

GPIO_SYSRESET_SEL_CR 0x58 RW-P Register PORESET_N Configures GPIO system reset

GPIN_SRC_SEL_CR 0x5C RW-P Register PORESET_N GPIO Input Source Select

Control Register

MDDR_CR 0x60 RW-P Register PORESET_N MDDR Configuration Register

USB_IO_INPUT_SEL_CR 0x64 RW-P Register PORESET_N Configures USB data interfaces

from IOMUXCELLs and I/O

pads

PERIPH_CLK_MUX_SEL_CR 0x68 RW-P Register PORESET_N Peripheral Clock MUX Select

Control Register

WDOG_CR 0x6C RW-P Register PORESET_N Configures Watchdog timer

MDDR_IO_CALIB_CR 0x70 RW-P Register PORESET_N MDDR I/O Calibration Control

Register

Reserved 0x74

EDAC_IRQ_ENABLE_CR 0x78 RW-P Register SYSRESET_

N

Enables/disables 1-bit error, 2-

bit error status for eSRAM0,

eSRAM1, USB, CAN, and MAC

USB_CR 0x7C RW-P Register SYSRESET_

N

Configures USB interface

ESRAM_PIPELINE_CR 0x80 RW-P Register SYSRESET_

N

Controls the pipeline present in

the memory read path of

eSRAM memory

MSS_IRQ_ENABLE_CR 0x84 RW-P Register SYSRESET_

N

MSS Interrupt Enable Control

Register

RTC_WAKEUP_CR 0x88 RW-P Register SYSRESET_

N

Configures RTC timer WAKEUP

signal

Table 650 • SYSREG (continued)

Register Name

Addr.

Offset

Register

Type

Flash

Write

Protect Reset Source Description

Loading...

Loading...