System Timer

UG0331 User Guide Revision 15.0 628

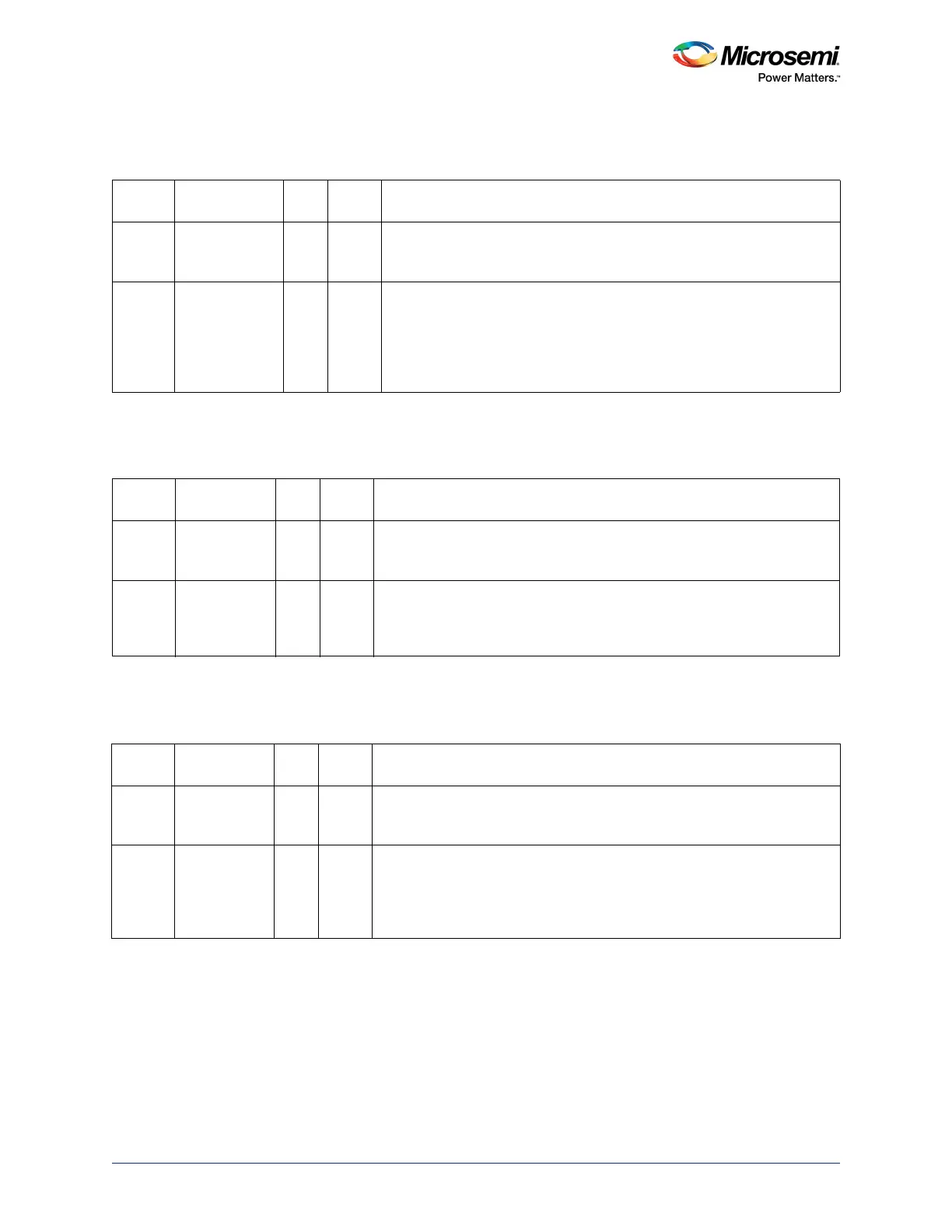

19.4.13 Timer 64 Raw Interrupt Status Register

19.4.14 Timer 64 Masked Interrupt Status Register

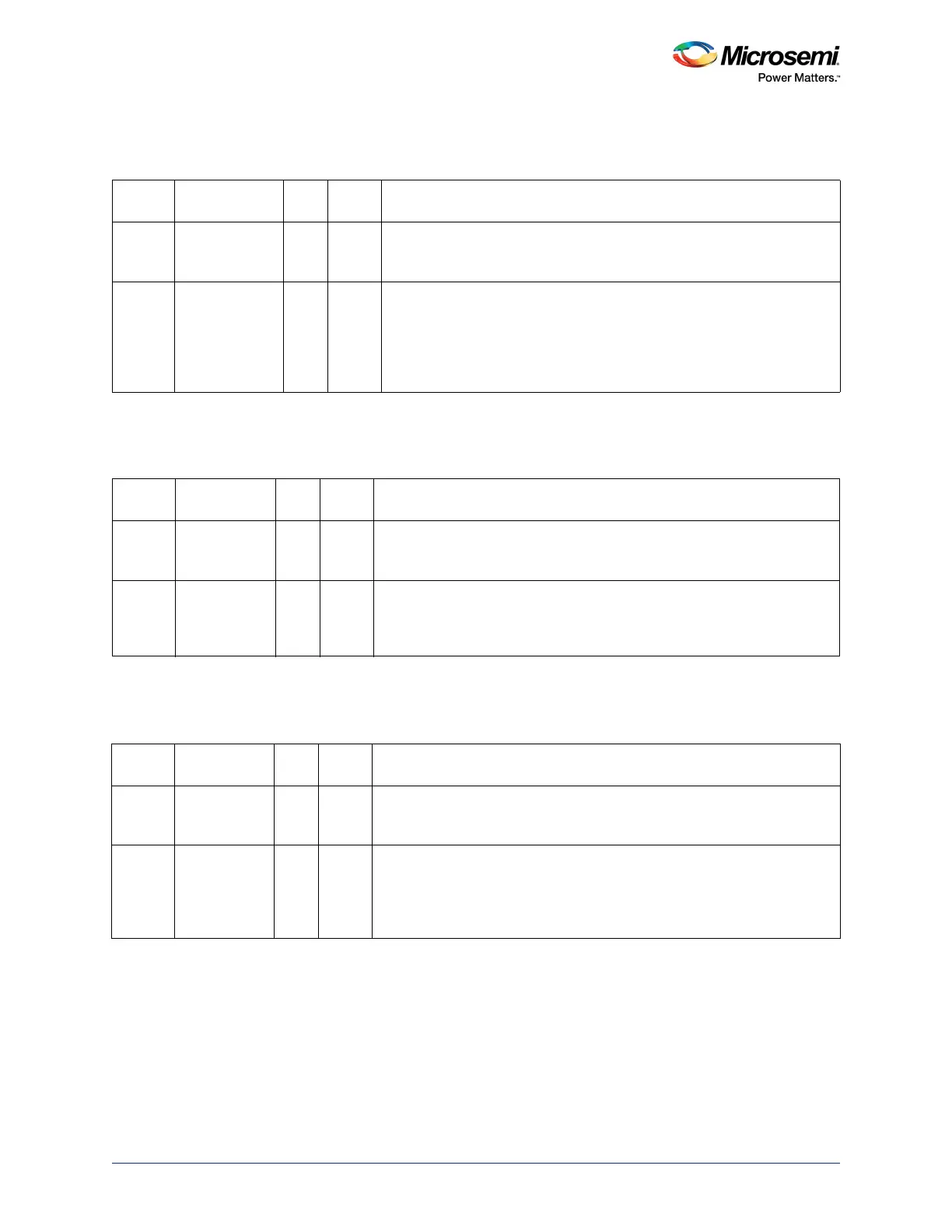

19.4.15 Timer 64 Mode Register

Table 630 • TIM64_RIS

Bit

Number Name R/W

Reset

Value Description

31:1 Reserved R/W 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0 TIM64_RIS R/W 0 Raw interrupt status (RIS) for 64-bit Timer mode.

0: Timer 64 has not reached zero

1: Timer 64 has reached zero at least once since this bit was last cleared

(by a reset or by writing 1 to this bit).

Writing 1 to this bit clears the bit and the interrupt; writing a zero has no

effect.

Table 631 • TIM64_MIS

Bit

Number Name R/W

Reset

Value Description

31:1 Reserved R 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0 TIM64_MIS R 0 Timer 64 masked interrupt status.

This read only bit is a logical AND of the TIM64RIS and TIM64INTEN bits.

The TIMER64INT output from the Timer has the same value as this bit.

Writing to this bit has no effect.

Table 632 • TIM64_MODE

Bit

Number Name R/W

Reset

Value Description

31:1 Reserved R/W 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

0 TIM64_MODE R/W 0 Timer 64 mode.

0: Timer 64 disabled; two separate 32-bit Timers.

1: Timer 64 enabled; one 64-bit Timer.

Changing the state of this bit has the effect of reinitializing the Timer

register map to its default power-up state.

Loading...

Loading...