CAN Controller

UG0331 User Guide Revision 15.0 467

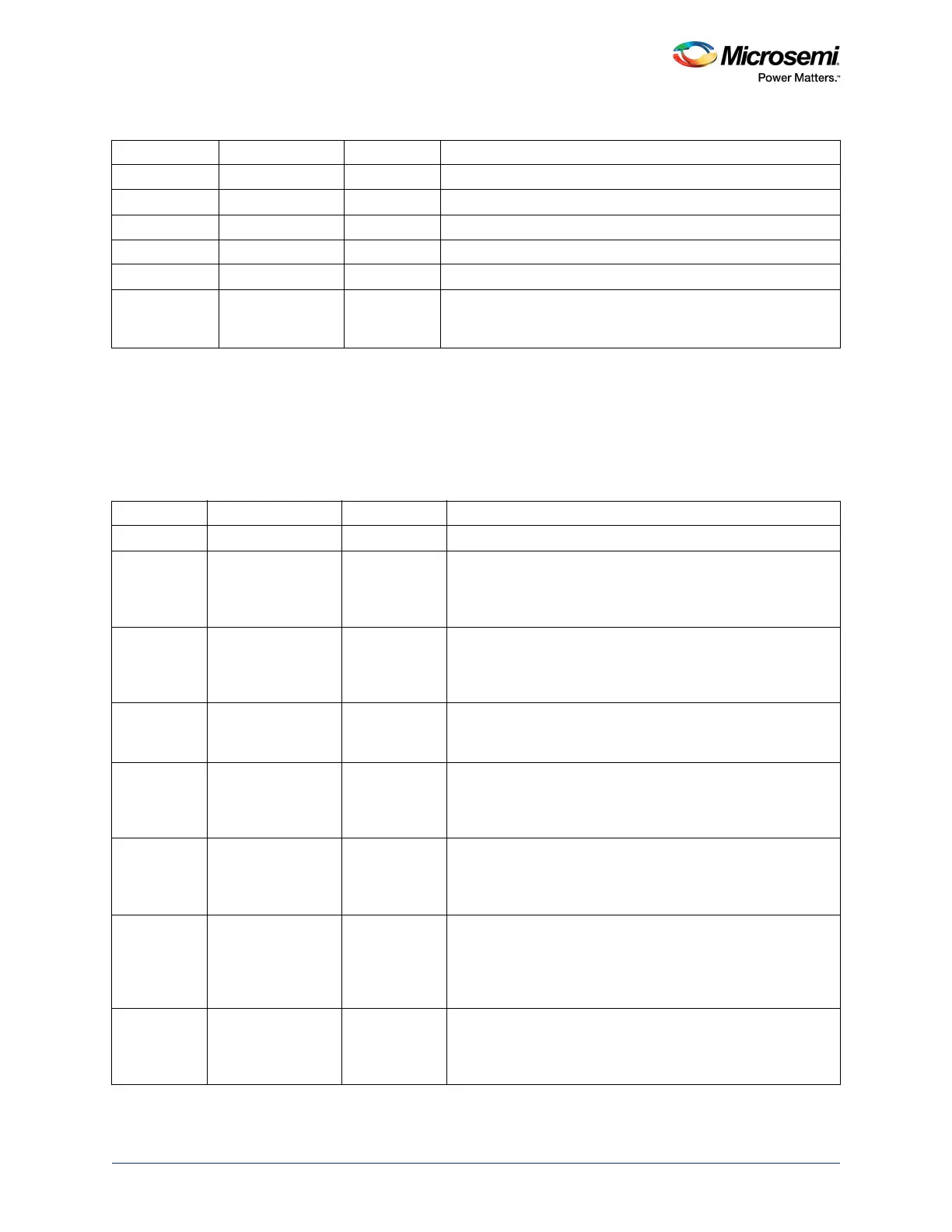

12.6.11.2 Interrupt Status Register

The interrupt status register stores internal interrupt events. Once a bit is set, it remains set until it is

cleared by writing 1 to it. The interrupt enable register has no effect on the interrupt status register. The

following table provides INT_STATUS register bit descriptions. A pending interrupt indicates that its

respective flag is set to 1. In order for an interrupt to be acknowledged, set its flag to 1.

5 stuff_err_enbl 0 Bit stuffing error interrupt enable.

4 bit_err_enbl 0 Bit error interrupt enable.

3 ovr_load_enbl 0 Overload message detected interrupt enable.

2 arb_loss_enbl 0 Arbitration loss interrupt enable.

1 Reserved 0 Reserved

0 Int_enbl 0 Global interrupt enable flag.

0: All interrupts are disabled

1: Enabled interrupt sources are available

Table 463 • INT_STATUS

Bit Number Name Reset Value Description

[31:16] Reserved 0 Reserved

15 SST_FAILURE 0 Single-shot transmission failure

0: Normal operation

1: A buffer set for single shot transmission experienced an

arbitration loss or a bus error during transmission.

14 STUCK_AT_0 0 Stuck at dominant error

0: Normal operation

1: Indicates if receive (RX) input remains stuck at 0 (dominant

level) for more than 11 consecutive bit times.

13 RTR_MSG 0 RTR auto-reply message sent

0: Normal operation

1: Indicates that a RTR auto-reply message was sent.

12 RX_MSG 0 Receive message available

0: Normal operation

1: Indicates a new message was successfully received and

stored in a receive buffer which has its RxIntEbl flag asserted.

11 TX_MSG 0 Message transmitted

0: Normal operation

1: Indicates a message was successfully sent from a transmit

buffer which has its TxIntEbl flag asserted.

10 RX_MSG_LOSS 0 Received message lost

0: Normal operation

1: Indicates a newly received message couldn't be stored

because the target message buffer was full (for example, its

MsgAv flag was set).

9 BUS_OFF 0 Bus Off

0: Normal operation

1: Indicates that the CAN controller entered the bus-off error

state.

Table 462 • INT_ENABLE (continued)

Bit Number Name Reset Value Description

Loading...

Loading...