MSS GPIO

UG0331 User Guide Revision 15.0 576

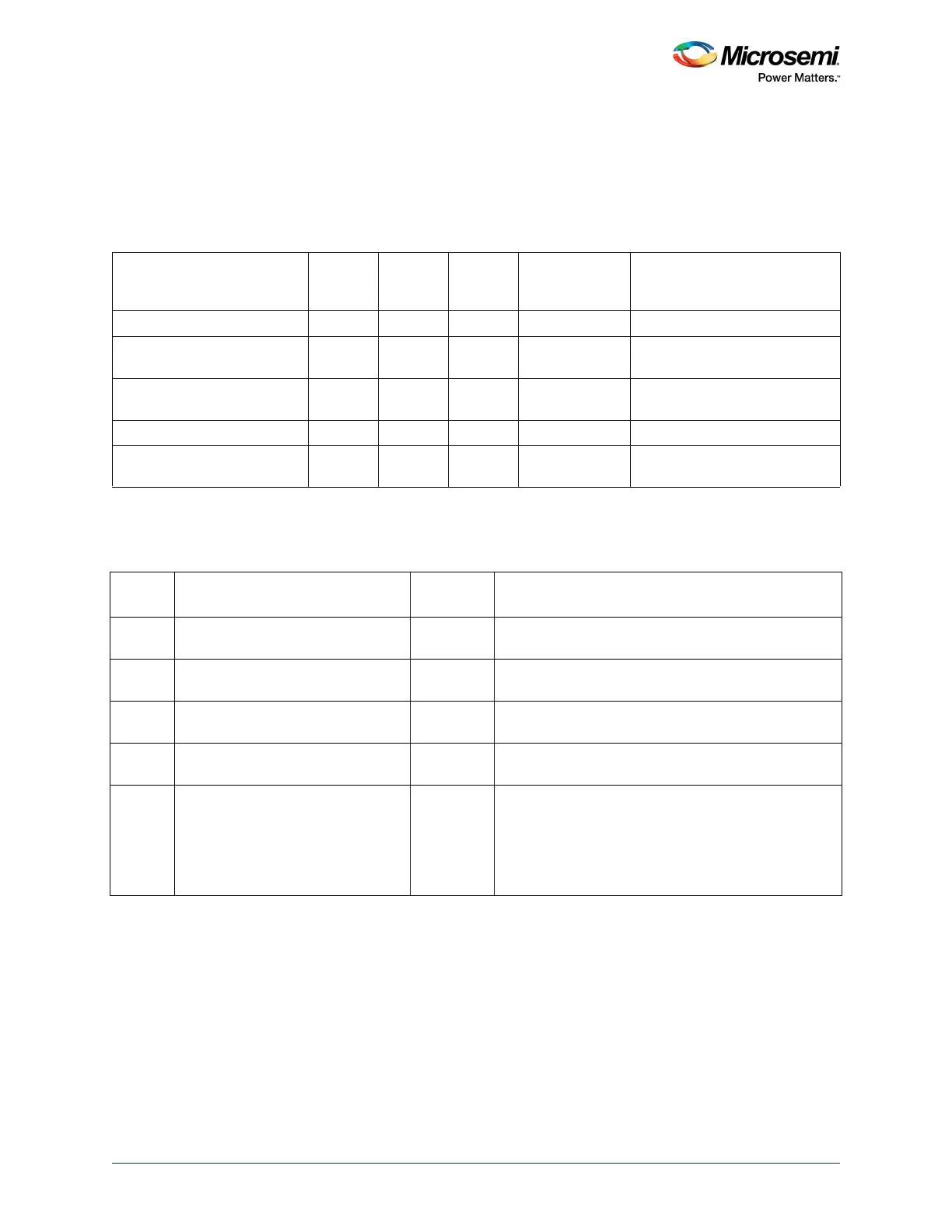

16.4.1 SYSREG Block Registers

16.4.1.1 Register Map

The following table lists all the GPIO registers in the SYSREG block. The SYSREG block is located at

address 0x40038000 in the Cortex-M3 processor address space.

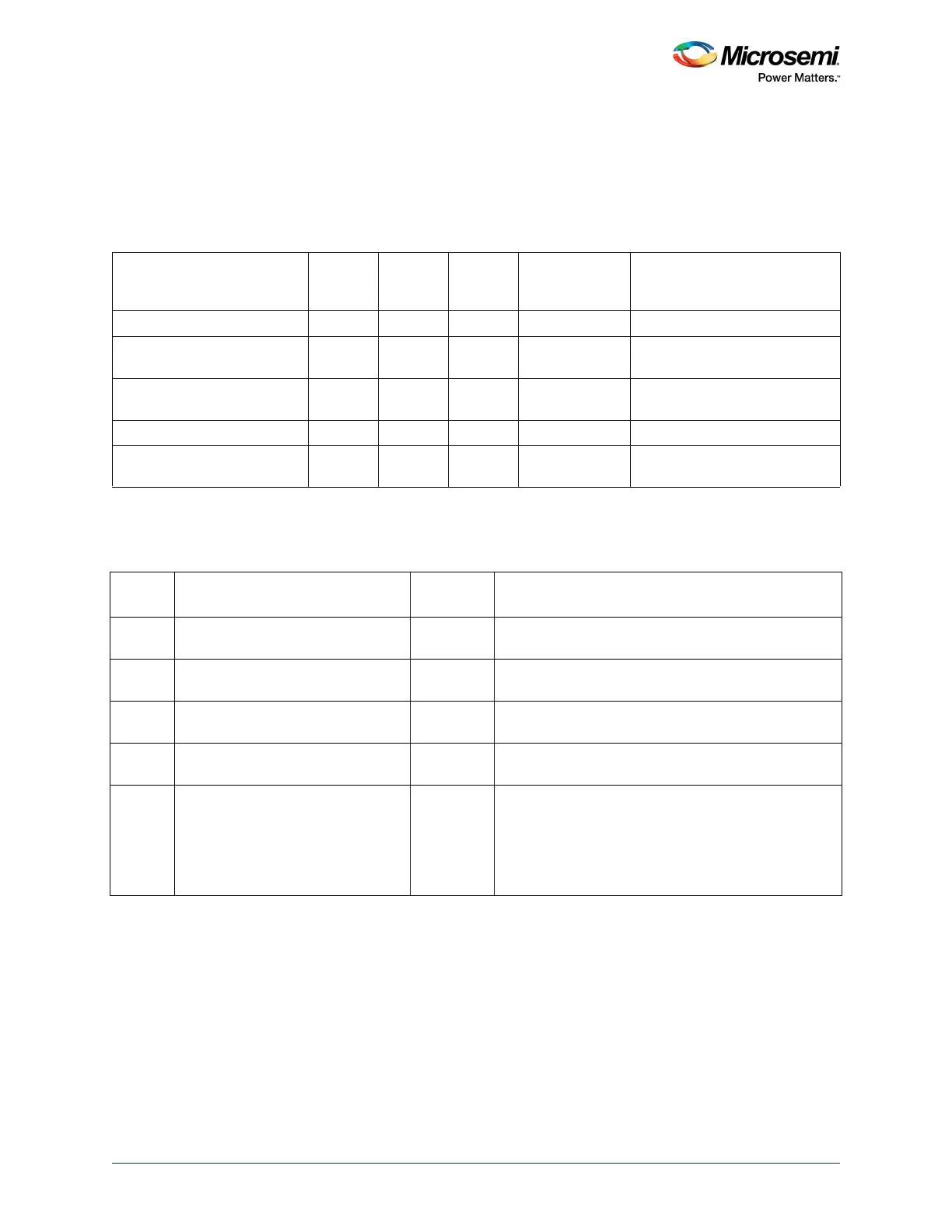

16.4.2 Software Reset Control Register

Table 539 • GPIO SYREG Registers

Register Name

Address

Offset

Register

Type

Flash

Write

Protect Reset Source Description

MSS_GPIO_DEF 0x18C RO-P SYSRESET_N MSS GPIO definition register

SOFT_RESET_CR 0x48 RW-P Bit SYSRESET_N Generates software control

interrupts to the MSS peripherals

LOOPBACK_CR 0x54 RW-P Register SYSRESET_N Loopback control for MSS

peripherals

GPIO_SYSRESET_SEL_CR 0x58 RW-P Register PORESET_N Configures GPIO system reset.

GPIN_SRC_SEL_CR 0x5C RW-P Register PORESET_N Used to generate a GPIO input

signal

Table 540 • SOFT_RESET_CR

Bit

Number Name

Reset

Value Description

24 MSS_GPOUT_31_24_SOFTRESET 0x1 0: Releases GPIO_OUT[31:24] from reset

1: Keeps GPIO_OUT[31:24] in reset

23 MSS_GPOUT_23_16_SOFTRESET 0x1 0: Releases GPIO_OUT[23:16] from reset

1: Keeps GPIO_OUT[23:16] in reset

22 MSS_GPOUT_15_8_SOFTRESET 0x1 0: Releases GPIO_OUT[15:8] from reset

1: Keeps GPIO_OUT[15:8] in reset

21 MSS_GPOUT_7_0_SOFTRESET 0x1 0: Releases GPIO_OUT[7:0] from reset

1: Keeps GPIO_OUT[7:0] in reset

20 MSS_GPIO_SOFTRESET 0x1 0: Releases the GPIO from reset, if not being held in

reset by some other means

1: Keeps the GPIO held in reset

Asserting this soft reset bit will hold the APB register,

GPIO input, and interrupt generation logic in reset.

GPIO OUT logic is not affected by this reset.

Loading...

Loading...