Watchdog Timer

UG0331 User Guide Revision 15.0 629

20 Watchdog Timer

The watchdog timer is an advanced peripheral bus (APB) slave that guards against the system crashes

by requiring regular service by the Cortex-M3 processor or by a bus master in the field programmable

gate array (FPGA) fabric.

20.1 Features

The watchdog timer has following features:

• A 32-bit timer counts down from a preset value to zero, then performs one of the following user-

configurable operations: If the counter is not refreshed, it will time out and either cause a system

reset or generate an interrupt to the processor.

• The watchdog timer counter is halted when the Cortex-M3 processor enters the debug state.

• The watchdog timer can be configured to generate a wake up interrupt when the Cortex-M3 is in

sleep mode.

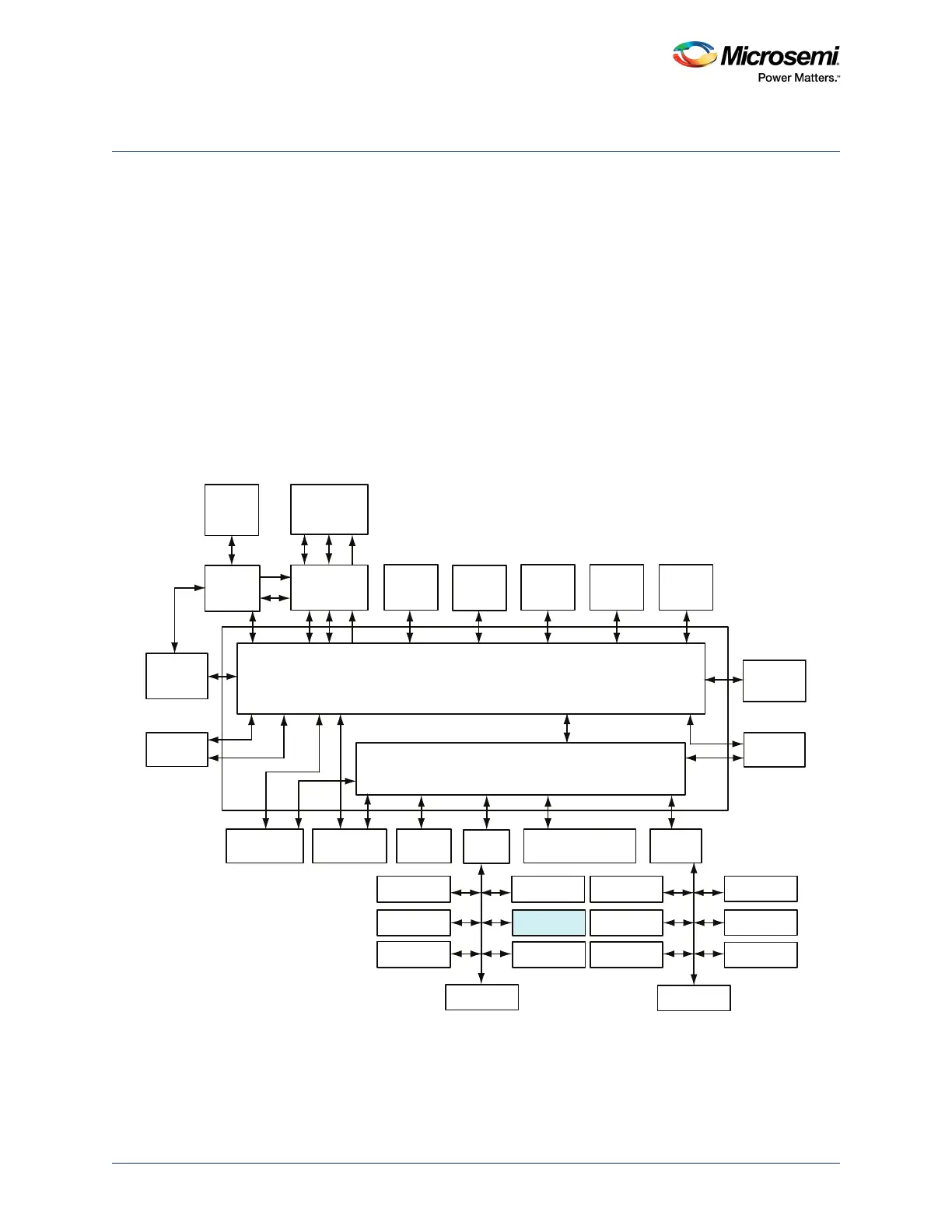

As shown in the following figure, the watchdog timer is connected to the AHB bus matrix through the

APB_0 interface.

Figure 267 • Microcontroller Subsystem Showing Watchdog Timer

AHB Bus Matrix

eSRAM_0

System

Controller

Cache

Controller

SD IC

ARM Cortex-M3

Processor

SDI

MSS DDR

Bridge

PDMA

MS6

MM3

AHB To AHB Bridge with Address Decoder

USB OTG

HPDMA

MDDR

APB_0

SYSREG

Triple Speed

Ethernet MAC

FIC_0

MM4 MS4

MS2 MS3 MS0

MS5

MS1

MM5 MM6

MM7

MM8

MM2 MM1 MM0 MM9

IDC

D/S

eNVM_0 eNVM_1 eSRAM_1

FIC_2 (Peripheral

Initialization)

APB_1

MMUART_0

SPI_0

I2C_0

PDMA

Configuration

WATCHDOG

FIIC

TIMERx2

MMUART_1

SPI_1

I2C_1

GPIO

CAN

RTC

COMM_BLK

FIC_1

MSS_FIC

MS6_USB

MS5_MAC MS5_SR MS5_APB0 MS5_FIC2 MS5_APB1

Loading...

Loading...