Ethernet MAC

UG0331 User Guide Revision 15.0 395

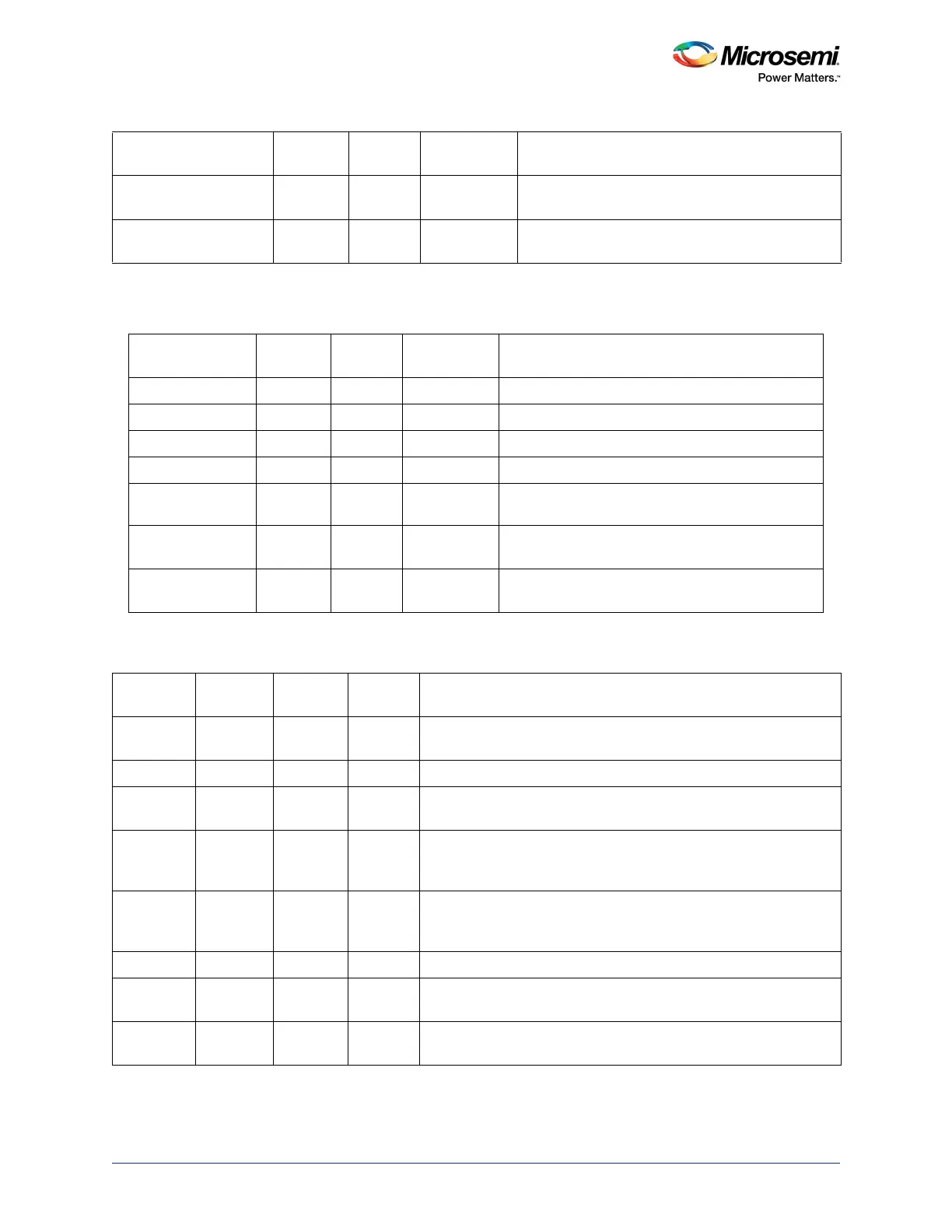

FIFO_RAM_ACCESS6 0x78 R/W 0x0 The FIFO RAM access register 6 is intended for

non-real-time RAM testing and debug.

FIFO_RAM_ACCESS7 0x7C RO 0x0 The FIFO RAM access register 7 is intended for

non-real-time RAM testing and debug.

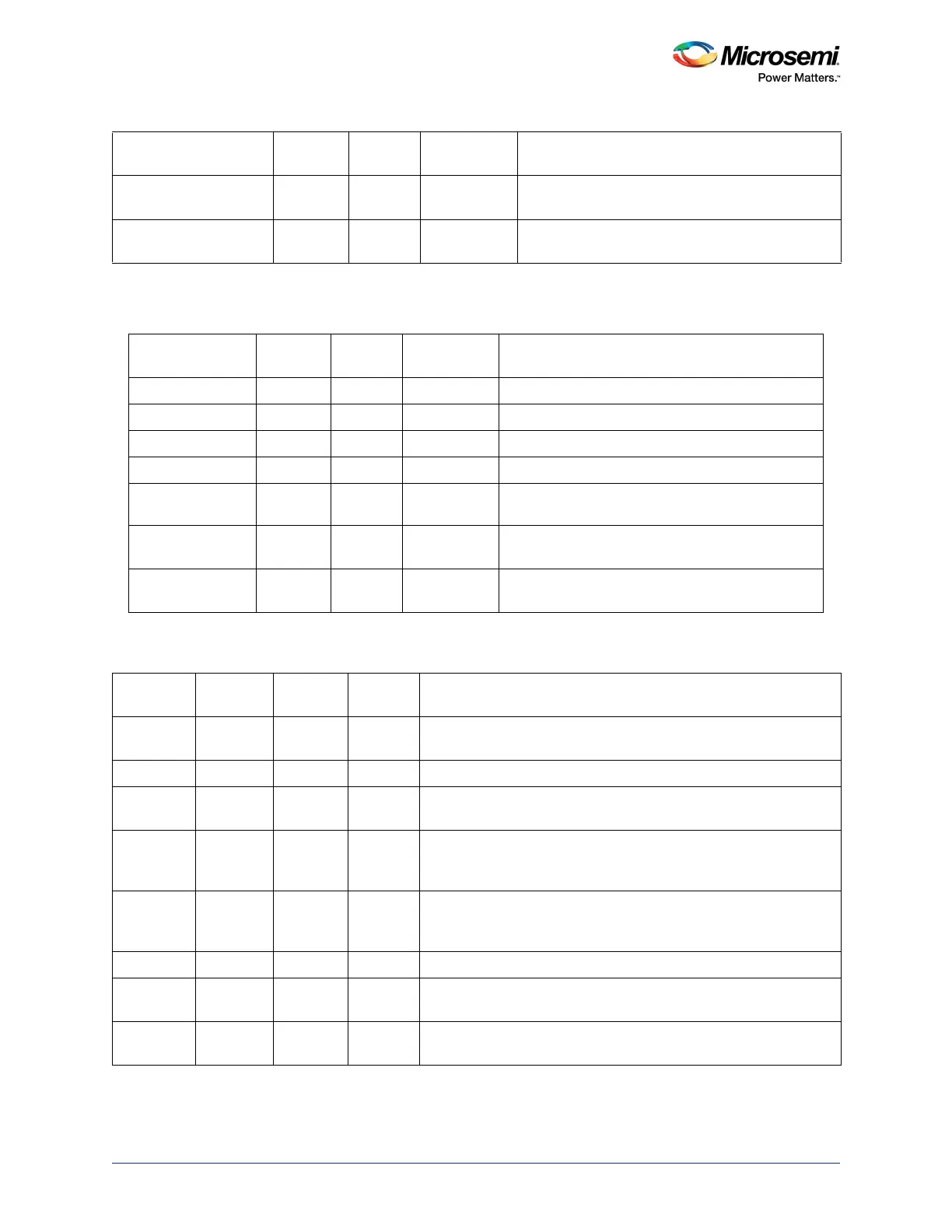

Table 335 • EMAC PE-MSTAT Transmit and Receive Counters Register Map

Register Name

Address

Offset

Register

Type Reset Value Description

TR64 0x80 R/W 0x0 Transmit and receive 64 byte frame counter

TR127 0x84 R/W 0x0 Transmit and receive 65 to127 byte frame counter

TR255 0x88 R/W 0x0 Transmit and receive 128 to 255 byte frame counter

TR511 0x8C R/W 0x0 Transmit and receive 256 to 511 byte frame counter

TR1K 0x90 R/W 0x0 Transmit and receive 512 to 1023 byte frame

counter

TRMAX 0x94 R/W 0x0 Transmit and receive 1024 to 1518 byte frame

counter

TRMGV 0x98 R/W 0x0 Transmit and receive 1519 to 1522 byte good VLAN

frame count

Table 336 • EMAC PE-MSTAT Receive Counters Register Map

Register

Name

Address

Offset

Register

Type

Reset

Value Description

RBYT 0x9C R/W 0x0 The statistic counter register is incremented by the byte count of all

frames received.

RPKT 0XA0 R/W 0x0 Incremented for each frame received packet.

RFCS 0XA4 R/W 0x0 This is incremented for each frame received that has an integral 64

to 1518 length and contains a frame check sequence error.

RMCA 0XA8 R/W 0x0 This is incremented for each multicast good frame of lengths

smaller than 1518 (non VLAN) or 1522 (VLAN) excluding

broadcast frames.

RBCA 0xAC R/W 0x0 This is incremented for each broadcast good frame of lengths

smaller than 1518 (non VLAN) or 1522 (VLAN) excluding multicast

frames.

RXCF 0XB0 R/W 0x0 This is incremented for each MAC control frame received.

RXPF 0XB4 R/W 0x0 This is incremented each time a valid PAUSE MAC control frame is

received.

RXUO 0XB8 R/W 0x0 This is incremented each time a MAC control frame is received

which contains an op code other than a PAUSE.

Table 334 • EMAC A-MCXFIFO Register Map (continued)

Register Name

Address

Offset

Register

Type Reset Value Description

Loading...

Loading...