Reset Controller

UG0331 User Guide Revision 15.0 654

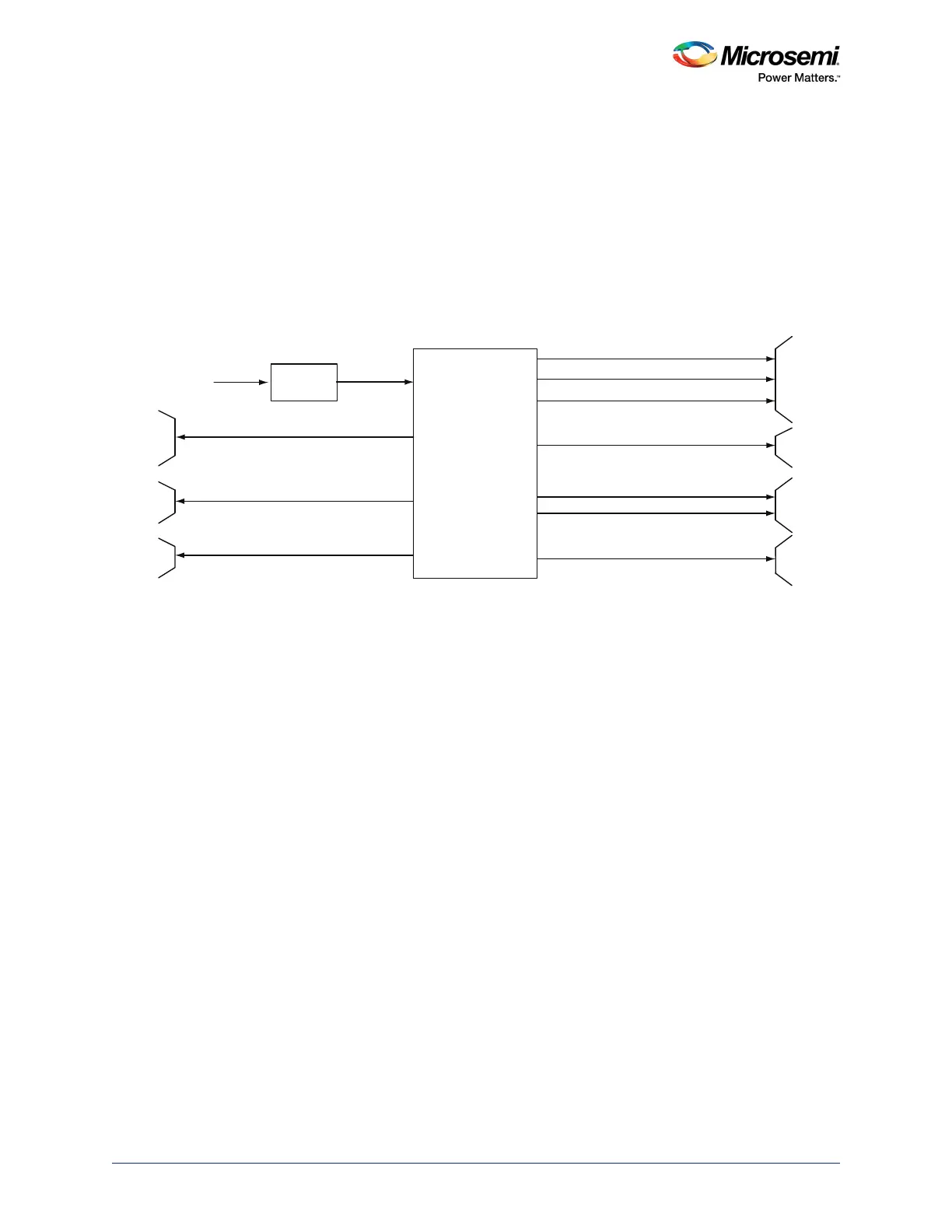

21.2.4 Power-On Reset

The Reset Controller receives a power-on reset signal, PO_RESET_N, from the System Controller,

which is a cold reset signal. Its assertion initializes the SmartFusion2 device to its default reset state.

PO_RESET_N signal is fed to the system register block (SYSREG). The PO_RESET_DETECT bit of the

RESET_SOURCE_CR register (defined in Table 648, page 669) in the SYSREG block is set or reset

depending on the PORESET_N signal.

The PORESET_N signal is a synchronized version of the PO_RESET_N signal on M3_CLK.

The Reset Controller generates different synchronized resets to the MSS and the FPGA fabric on the

assertion of PO_RESET_N, as shown in the following figure.

Figure 285 • Functional Block Diagram of Reset Controller During Power-On Reset

The CC_RESET_N is generated on the assertion of PO_RESET_N. This is a power-on reset signal to

the fabric alignment clock controller (FACC).

21.2.5 System Reset

The system reset (SYSRESET_N) is generated if any of the following conditions are true:

• SYS_RESET_REQ is asserted from Cortex-M3 processor. SYS_RESET_REQ from the

Cortex-M3 processor is controlled by the SYSRESETREQ bit in the Application Interrupt and the

Reset Control register located at 0XE000ED0C. For more information, refer to Cortex-M3 Processor

(Reference Material), page 18.

• LOCKUP_N is asserted from Cortex-M3 processor in the LOCKUP state. The processor enters into

LOCKUP state, if a fault occurs when executing the NMI or HardFault handlers.

• Watchdog timeout event from the Watchdog Timer.

• SC_MSS_RESET_N is asserted from the System Controller during the start-up sequence after

power-up.

• MSS_RESET_N_F2M is asserted from the FPGA fabric interface.

Reset Controller

Watchdog

Timer

Peripherals

MDDR

PORESET_RCOSC_N

SYSREG

PORESET

_

N

MSS GPIO

MSS

_

GPIO

_

RESET

_

N

Cortex -M3

M

3_

PORESET

_

M

3_

CLK

_

N

M

3_

PORESET

_

TCK

_

N

T_ RESET_N

CC

_

RESET

_

N

FACC

MDDR

_

APB

_

RESET

_

N

MDDR_ AXI_RESET_ N

Block resets

/

System

Controller

PO_RESET_N

Processor

DEVRST_N

Loading...

Loading...