Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 47

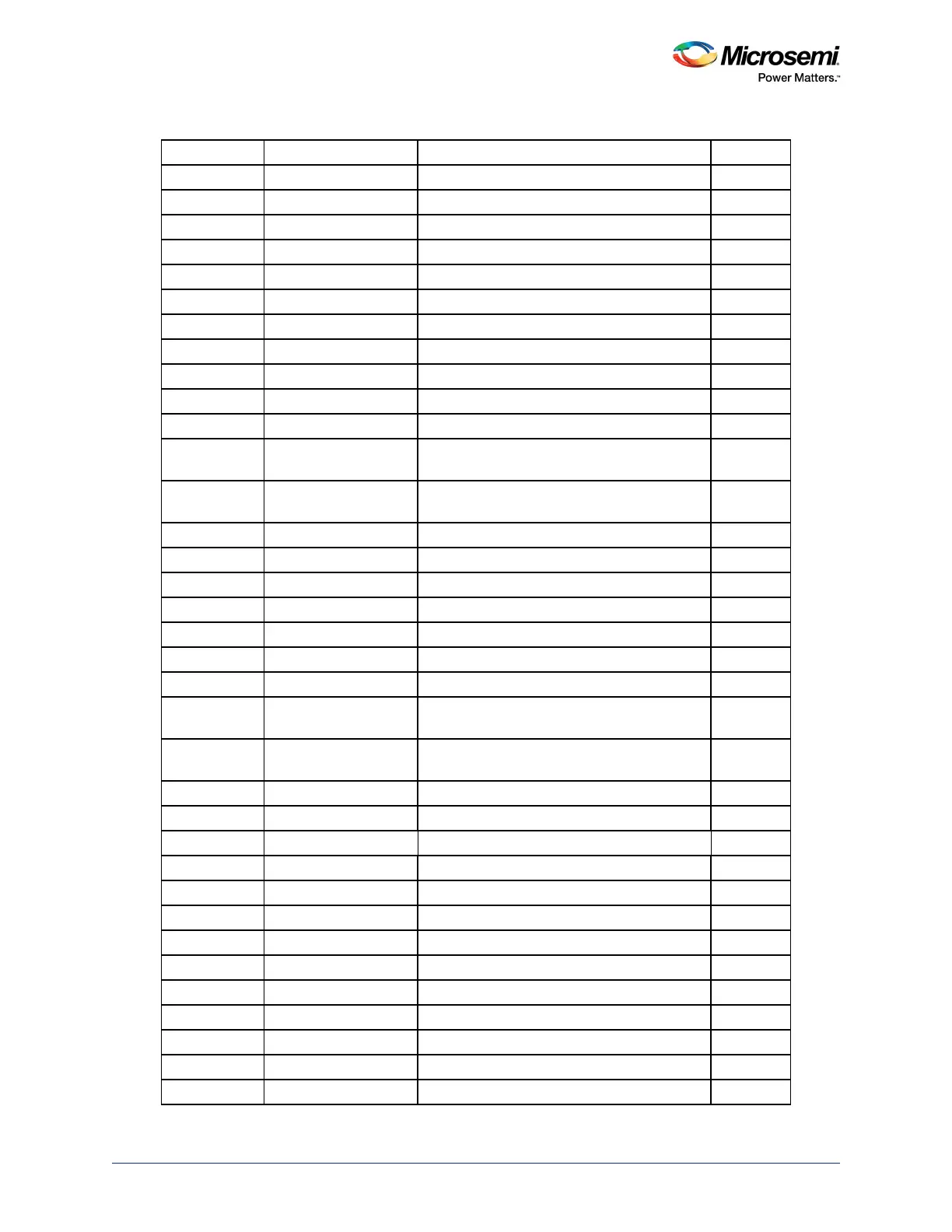

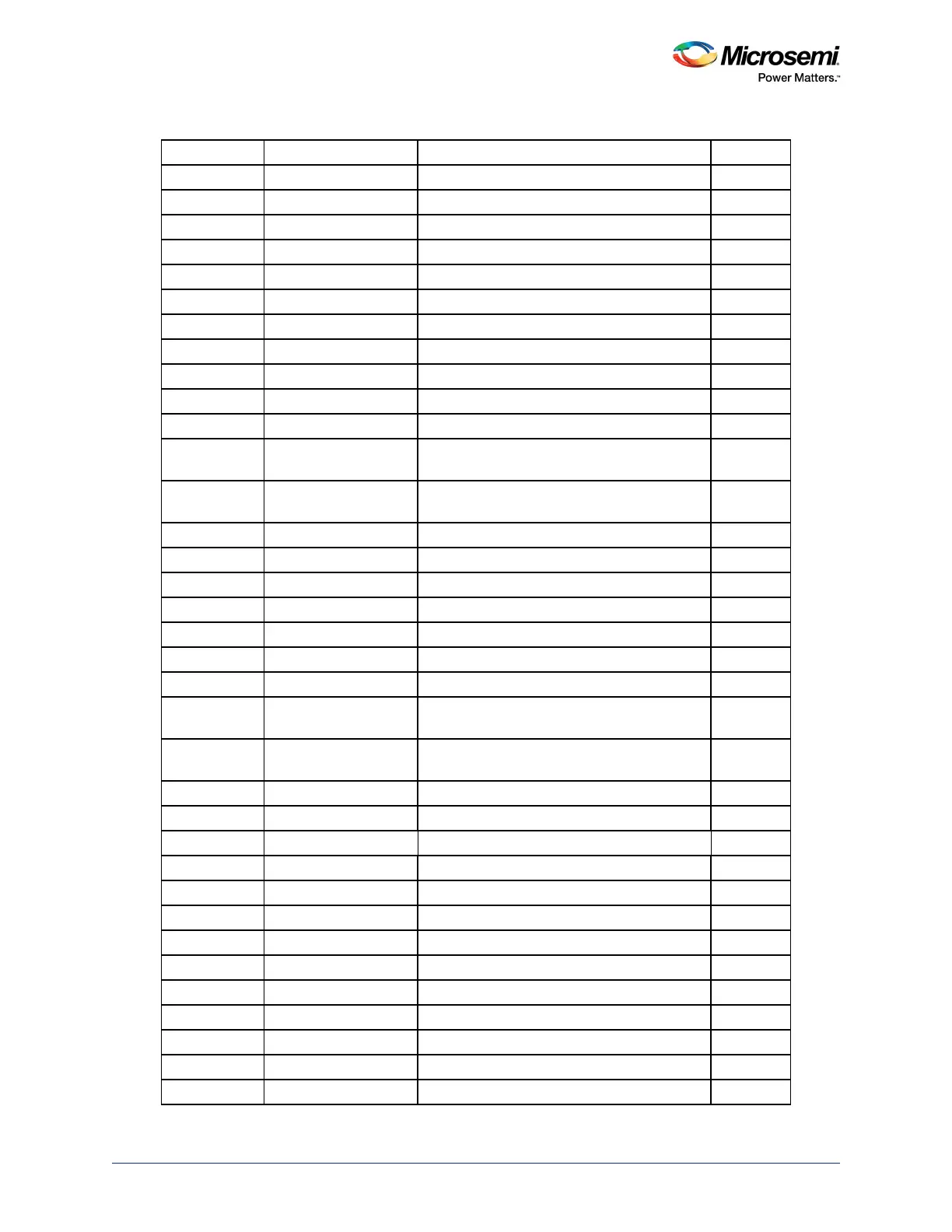

CLZ Rd, Rm Count Leading Zeros

CMN Rn, Op2 Compare Negative N, Z, C, V

CMP Rn, Op2 Compare N, Z, C, V

CPSID i Change Processor State, Disable Interrupts

CPSIE i Change Processor State, Enable Interrupts

DMB Data Memory Barrier

DSB Data Synchronization Barrier

EOR, EORS {Rd,} Rn, Op2 Exclusive OR N, Z, C

ISB Instruction Synchronization Barrier

IT If-Then condition block

LDM Rn{!}, reglist Load Multiple registers, increment after

LDMDB,

LDMEA

Rn{!}, reglist Load Multiple registers, decrement before

LDMFD,

LDMIA

Rn{!}, reglist Load Multiple registers, increment after

LDR Rt, [Rn, #offset] Load Register with word

LDRB, LDRBT Rt, [Rn, #offset] Load Register with byte

LDRD Rt, Rt2, [Rn, #offset] Load Register with two bytes

LDREX Rt, [Rn, #offset] Load Register Exclusive

LDREXB Rt, [Rn] Load Register Exclusive with Byte

LDREXH Rt, [Rn] Load Register Exclusive with Halfword

LDRH, LDRHT Rt, [Rn, #offset] Load Register with Halfword

LDRSB,

LDRSBT

Rt, [Rn, #offset] Load Register with Signed Byte

LDRSH,

LDRSHT

Rt, [Rn, #offset] Load Register with Signed Halfword

LDRT Rt, [Rn, #offset] Load Register with word

LSL, LSLS Rd, Rm, <Rs|#n> Logical Shift Left N, Z, C

LSR, LSRS Rd, Rm, <Rs|#n> Logical Shift Right N, Z, C

MLA Rd, Rn, Rm, Ra Multiply with Accumulate, 32-bit result

MLS Rd, Rn, Rm, Ra Multiply and Subtract, 32-bit result

MOV, MOVS Rd, Op2 Move N, Z, C

MOVT Rd, #imm16 Move Top

MOVW, MOV Rd, #imm16 Move 16-bit constant N, Z, C

MRS Rd, spec_reg Move from Special Register to general register

MSR spec_reg, Rm Move from general register to Special Register N, Z, C,V

MUL, MULS {Rd,} Rn, Rm Multiply, 32-bit result N, Z

MVN, MVNS Rd, Op2 Move NOT N, Z, C

NOP No Operation

Table 26 • Cortex-M3 Processor Instructions (continued)

Mnemonic Operands Brief description Flags

Loading...

Loading...