Fabric Interface Controller

UG0331 User Guide Revision 15.0 778

24.7.2.6 Step 6: Timing Analysis Requirements

Post-layout static timing analysis must be performed to make sure that the design meets the frequency

requirements defined in MSS_CCC and the fabric CCC configurator. M3_CLK may need to be changed

or clock ratio between M3_CLK and the FIC clocks increased to get a design that passes the static timing

analysis.

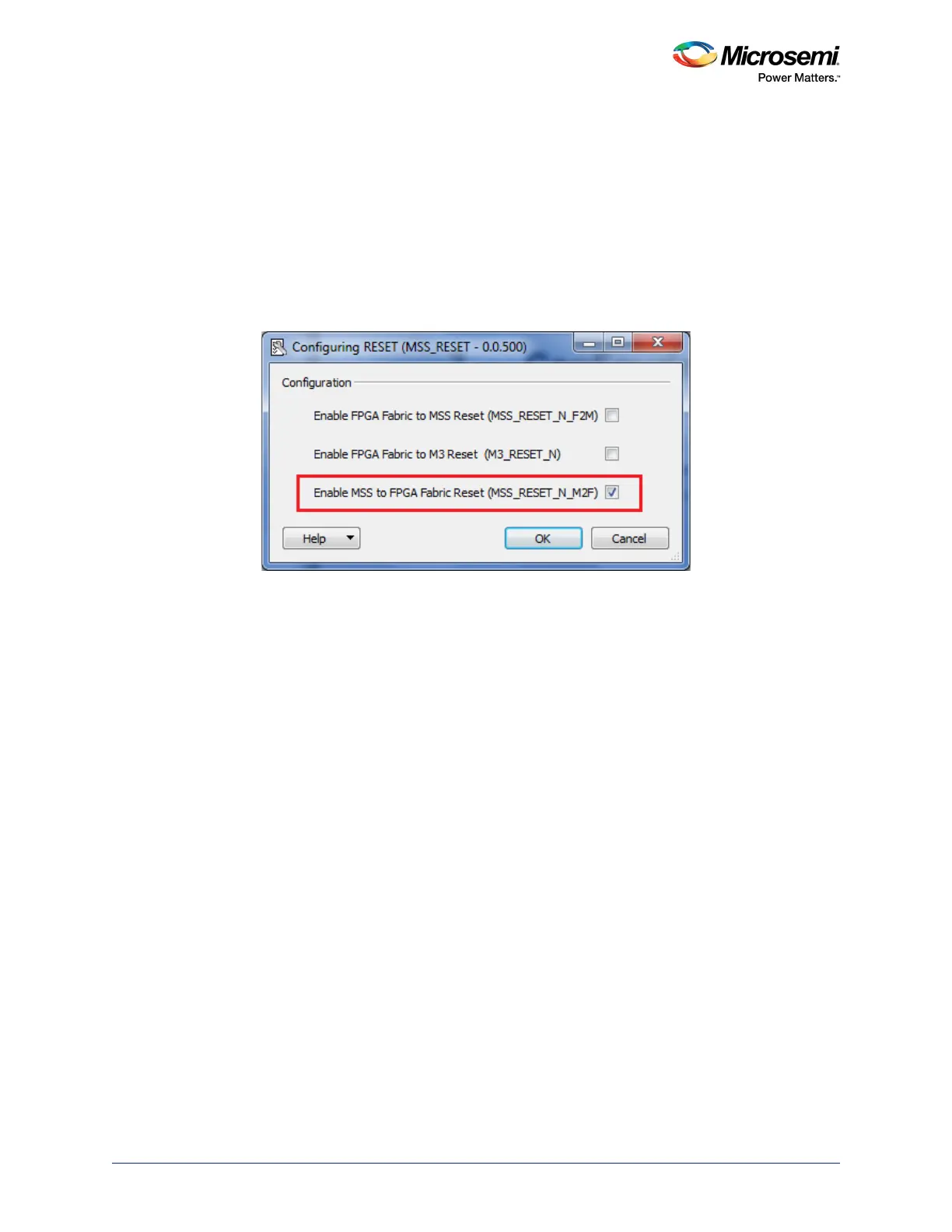

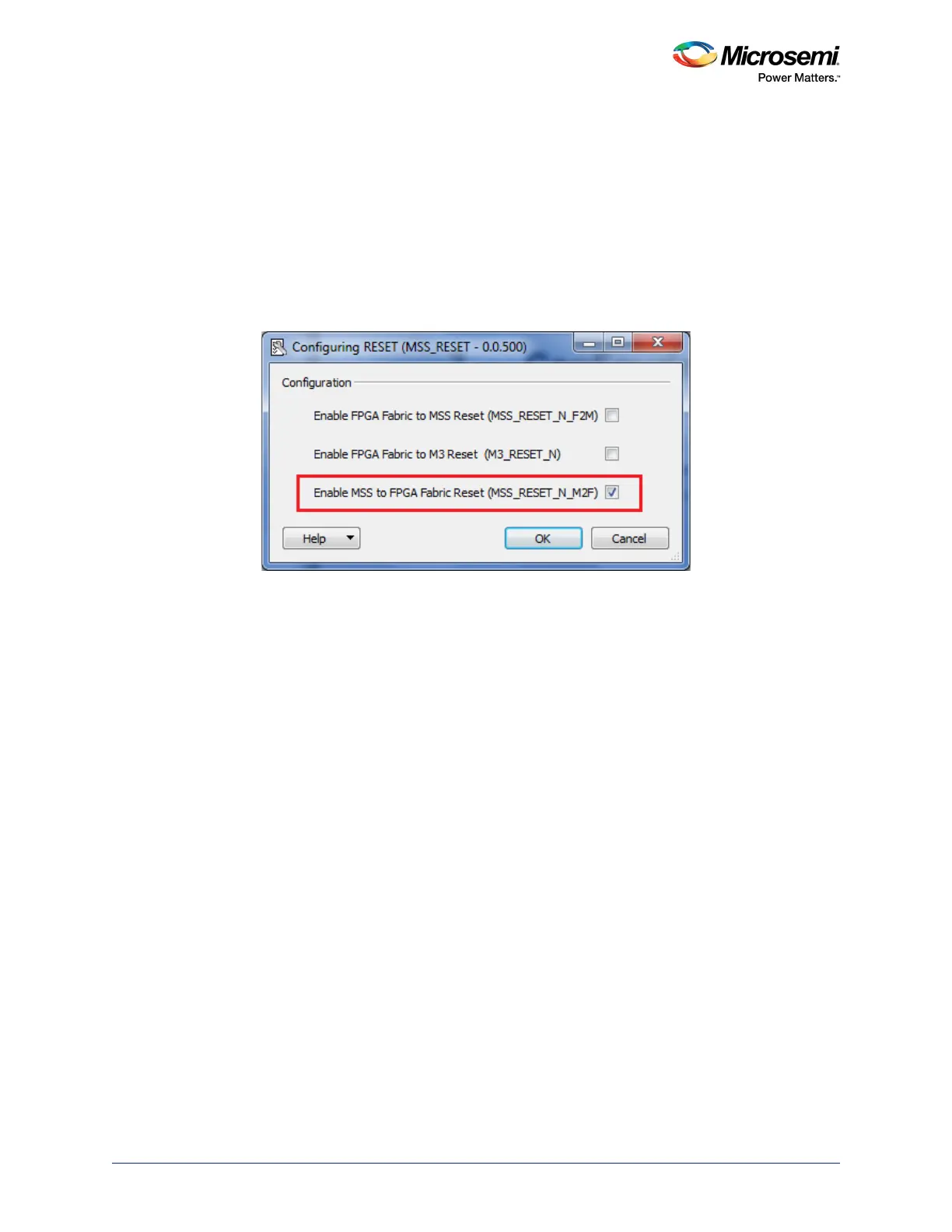

24.7.3 Configuring the FIC Subsystem Reset

To configure the FIC Subsystem reset:

1. Configure the MSS Reset sub-block to expose the MSS_RESET_N_M2F port, as shown in the

following figure.

Figure 352 • Configure the MSS Reset Sub-Block

2. Connect the MSS_RESET_N_M2F port to all the FPGA fabric FIC subsystems reset ports.

Loading...

Loading...