System Register Block

UG0331 User Guide Revision 15.0 699

22.3.29 Watchdog Configuration Register

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

Information about other WatchDog system registers is given in Table 745, page 727 and Table 746,

page 727.

22.3.30 MDDR I/O Calibration Control Register

22.3.31 EDAC Interrupt Enable Control Register

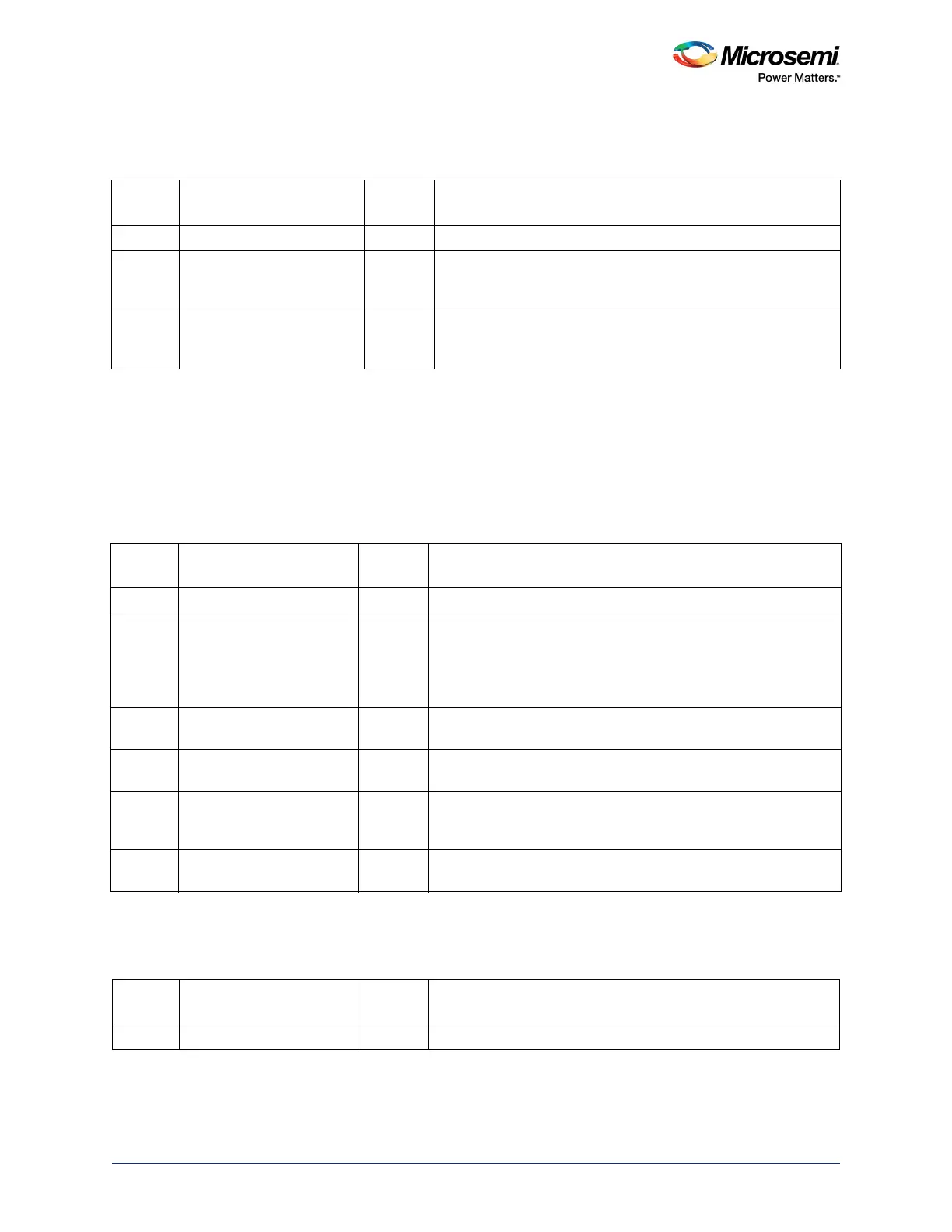

Table 683 • WDOG_CR

Bit

Number Name

Reset

Value Description

[31:2] Reserved 0

1 WDOGMODE 0 Resets/interrupts the mode selection bit from System Register.

This value can be read from the WDOGCONTROL register

within the WatchDog module.

0 WDOGENABLE 0 Enables the bit for Watchdog module. The status of this bit can

be monitored in the WDOGENABLE register within the

WatchDog module.

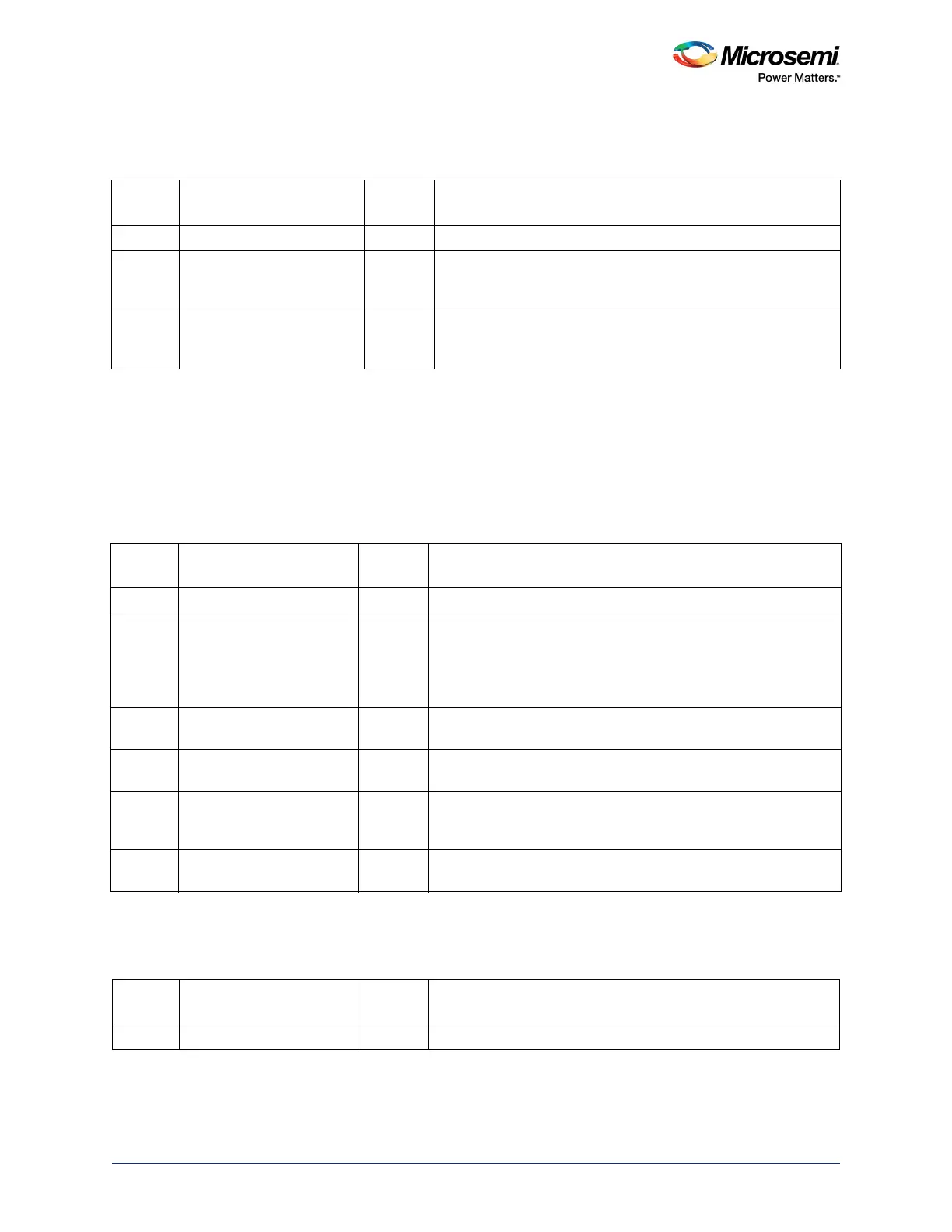

Table 684 • MDDR_IO_CALIB_CR

Bit

Number Name

Reset

Value Description

[31:15] Reserved 0

14 CALIB_LOCK 0 Used in the DDRIO calibration block as an override to lock the

codes during intermediate runs. When the firmware receives

CALIB_INTRPT, it may choose to assert this signal by prior

knowledge of the traffic without going through the process of

putting the DDR into self refresh. This bit is only read/write.

13 CALIB_START 0 Used in the DDRIO calibration block and indicates that rerun of

the calibration state machine is required.

12 CALIB_TRIM Used in the DDRIO calibration block and indicates the override of

the calibration value from the PC code/programmed code values.

[11:6] NCODE 0 Used in the DDRIO calibration block and indicates DPC override

NCODE from flash. This can also be overwritten from the

firmware.

[5:0] PCODE 0 Used in the DDRIO calibration block and indicates PC override

PODE from flash. This can also be overwritten from the firmware.

Table 685 • EDAC_IRQ_ENABLE_CR

Bit

Number Name

Reset

Value Description

[31:15] Reserved 0

Loading...

Loading...