Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 335

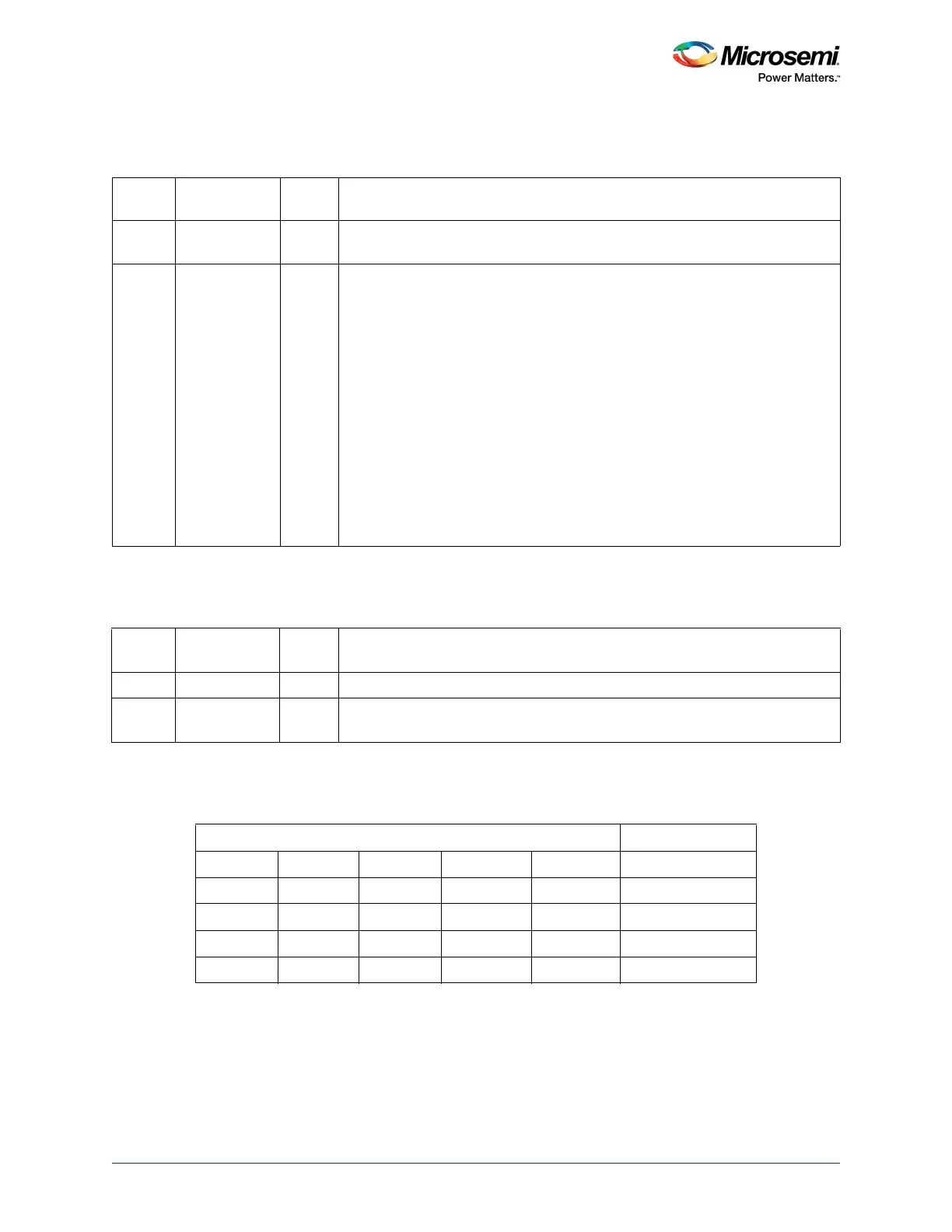

10.3.8.5 RX_FIFO_SIZE_REG Bit Definitions

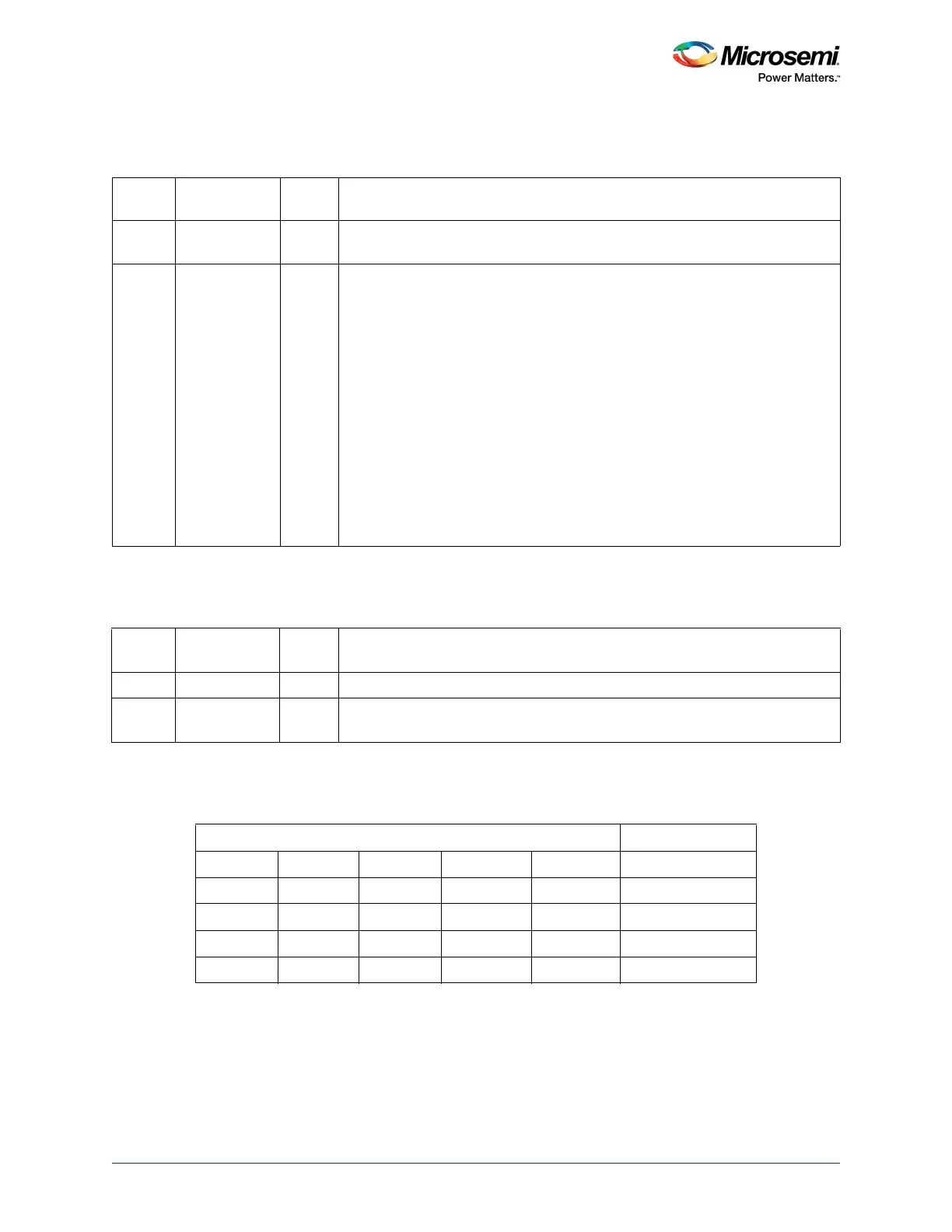

10.3.8.6 TX_FIFO_ADD_REG Bit Definitions

10.3.8.7 Start Address of Transmit Endpoint

Table 245 • RX_FIFO_SIZE_REG (0x40043063)

Bit

Number Name

Reset

Value Function

4 DPB 0 Defines whether double-packet buffering is supported. When ‘1’, double-packet

buffering is supported. When ‘0’, only single-packet buffering is supported.

[3:0] SZ[3:0] 0 Maximum packet size to be allowed for (before any splitting within the FIFO of

bulk/high-bandwidth packets prior to transmission).

00

00: 8 Bytes

0

001: 16 Bytes

0010: 32 Bytes

0011: 64 Bytes

0100: 128 Bytes

0101: 256 Bytes

0110: 512 Bytes

0111: 1,024 Bytes

1000: 2,048 Bytes

1001: 4,096 Bytes

If DPB = 0, the FIFO will also be this size; if DPB = 1, the FIFO will be twice this

size.

Table 246 • TX_FIFO_ADD_REG (0x40043064)

Bit

Number Name

Reset

Value Function

13 Reserved N/A

[12:0] AD[12:0] 0 Start address of the transmit endpoint FIFO in units of 8 bytes as given in

Table 247, page 336.

Table 247 • Start Address of Transmit Endpoint

AD[12:0] Start Address

0 0 … 0 0 0x0000

0 0 … 0 1 0x0008

0 0 … 1 0 0x0010

……

1 1 … 1 1 0xFFF8

Loading...

Loading...