Ethernet MAC

UG0331 User Guide Revision 15.0 429

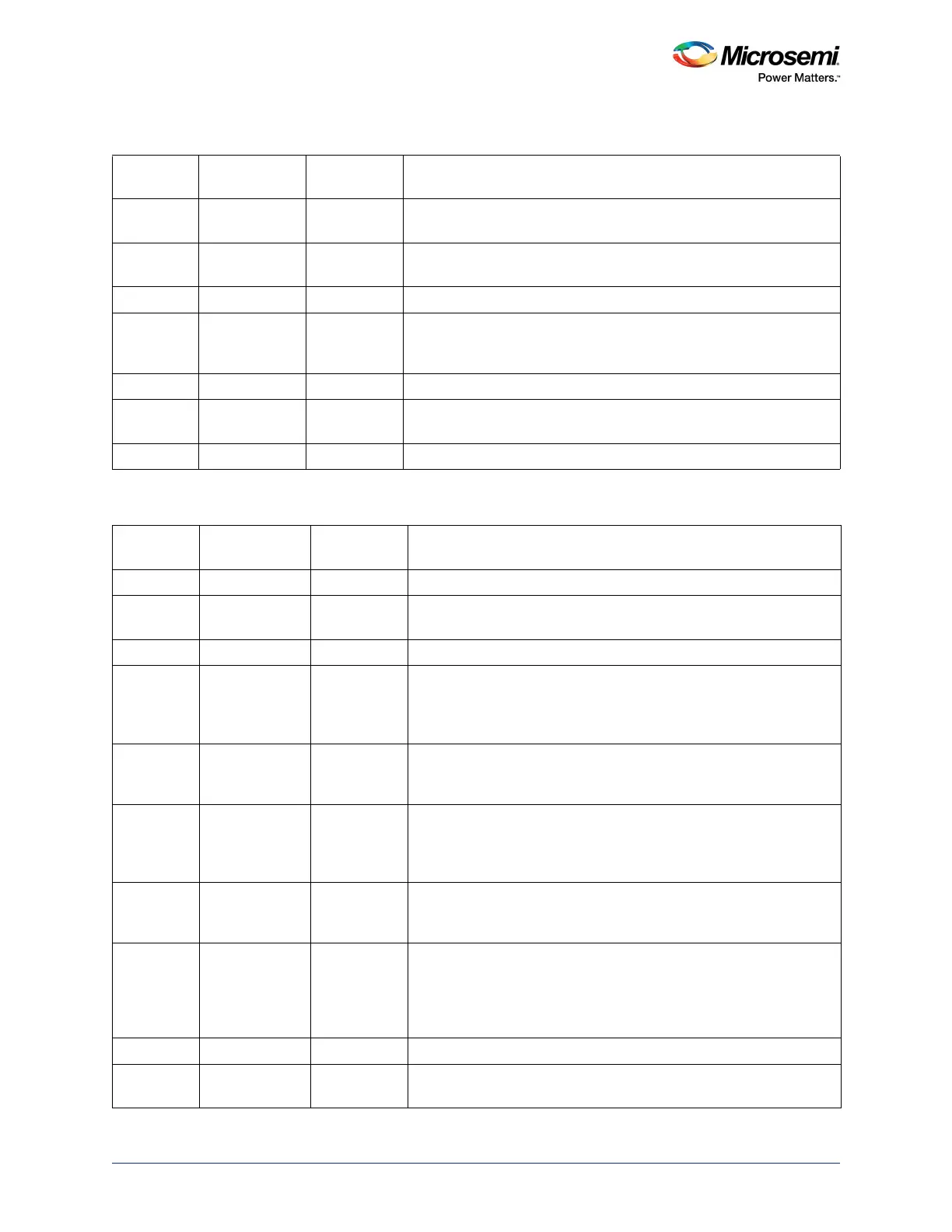

Table 425 • SGMII CONTROL

Bit Number Name

Reset

Value Description

15 PHY RESET 0x0 Setting this bit causes the PETEX, PEREX, and PEANX sub-modules

in the M-SGMII core to be reset. This bit is self-clearing.

14 LOOP BACK 0x0 Setting this bit causes the M-SGMII loopback. Clearing this bit results

in normal operation.

13 Reserved 0x0 Reserved.

12 AUTO-

NEGOTIATION

ENABLE

0x0 Setting this bit enables the auto-negotiation process.

[11:10] Reserved 0x0 Reserved.

9 RESET AUTO-

NEGOTIATION

0x0 Setting this bit causes the auto-negotiation process to restart. This

action is only available when auto-negotiation has been enabled.

[8:0] Reserved 0x0 Reserved

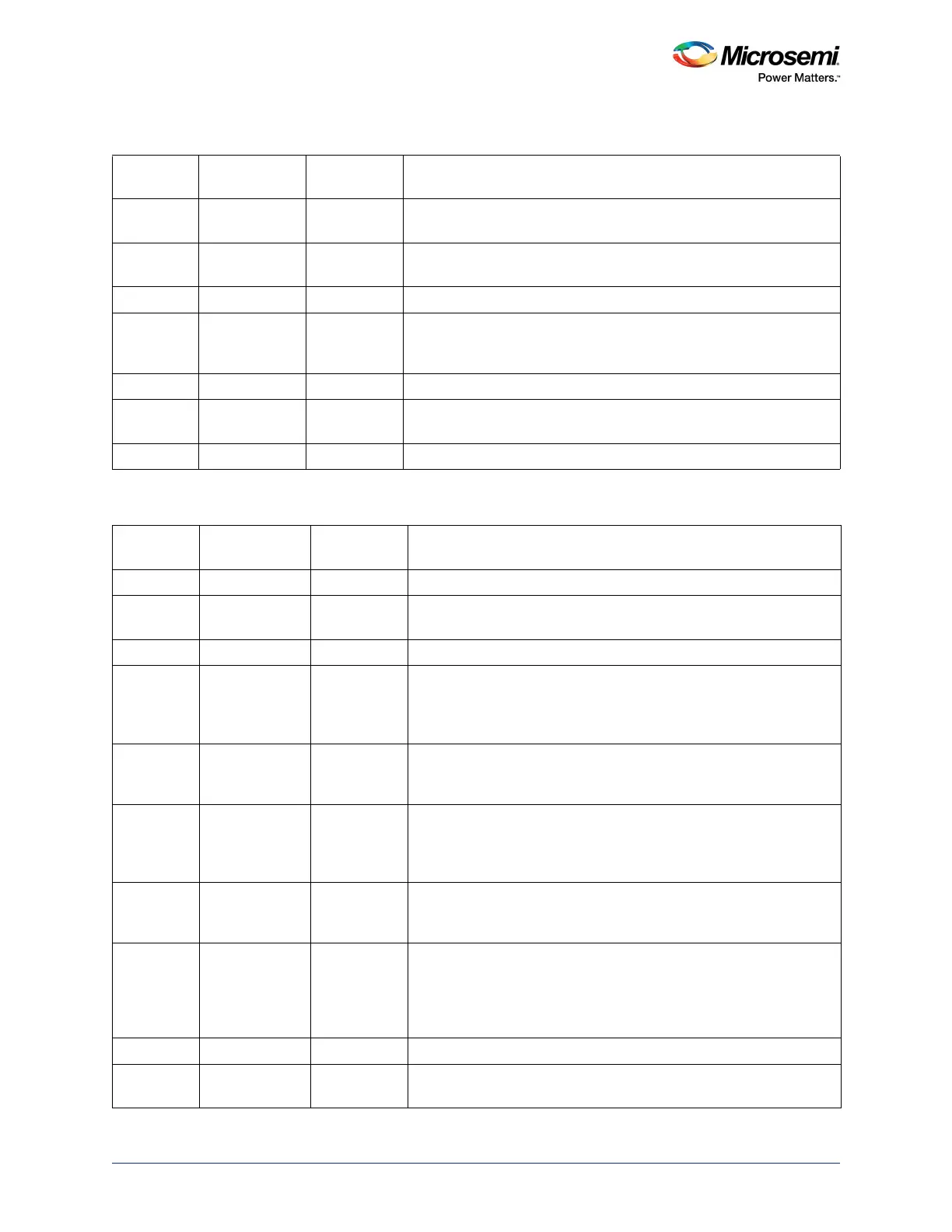

Table 426 • SGMII STATUS

Bit Number Name

Reset

Value Description

[15:9] Reserved 0x0 Reserved.

8 EXTENDED

STATUS

0x0 This bit returns ‘1’ on read to indicate that the PHY status information

is also contained in EXTENDED STATUS register.

7 Reserved 0x0 Reserved.

6 MF PREMABLE

SUPPRESSION

ENABLE

0x0 This bit indicates whether the PHY is capable of handling MII

management frames without the 32-bit preamble field.

Returns ‘1’ on read to indicate the support for suppressed preamble

MII management frames.

5AUTO-

NEGOTIATION

COMPLETE

0x0 This bit indicates that the Auto-negotiation process is completed.

Returns ‘0’ on read when either the auto-negotiation process is

underway or when the Auto-negotiation function is disabled.

4 REMOTE

FAULT

0x0 This bit returns ‘1’ on read to indicate a remote fault condition has

been detected between the M-SGMII and the PHY. This bit latches

high in order for software to detect the condition. Each read of the

STATUS register clears this bit.

3AUTO-

NEGOTIATION

ABILITY

0x0 When ‘1’, this bit indicates that the M-SGMII has the ability to

perform auto-negotiation. Returns ‘1’ on read.

2 LINK STATUS This bit indicates that a valid link is established between the

M-SGMII and the PHY.

Returns ‘0’ on read to indicate that there is no valid link is

established. This bit latches low to allow software polling to detect a

failure condition.

1 Reserved 0x0 Reserved

0 EXTENDED

CAPABILITY

0x1 This bit returns ‘1’ on read to indicates that the M-SGMII contains the

extended set of registers (those beyond CONTROL and STATUS).

Loading...

Loading...