Error Detection and Correction Controllers

UG0331 User Guide Revision 15.0 792

26 Error Detection and Correction Controllers

In SEU susceptible environments, which are increasingly more common at ground-level due to shrinking

geometries, storage elements such as RAMs and FIFOs in the microcontroller subsystem (MSS) are

susceptible to transient errors caused by heavy ions. Errors can be detected and corrected by employing

error detection and correction (EDAC). The EDAC controllers implemented in SmartFusion2 devices

support single error correction and double error detection (SECDED).

SmartFusion2 SOC memories such as eSRAM, cache, eNVM, USB internal memory, internal FIFOs of

the Ethernet MAC, and the internal RAM of the controller area network (CAN) controller are protected by

EDAC. Fabric SRAM blocks are not protected by EDAC.

26.1 Functional Description

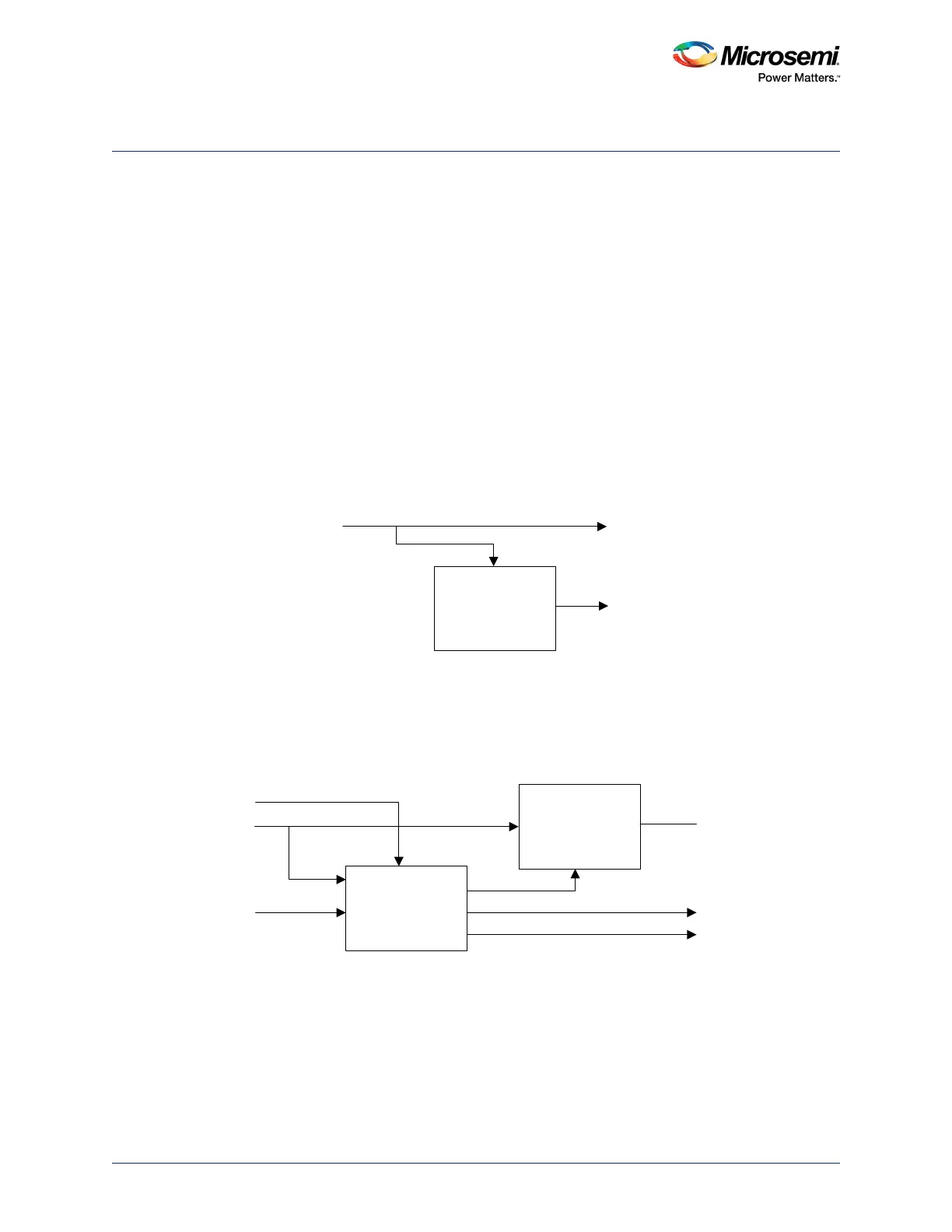

EDAC algorithms generate additional checksum bits for each data word to be stored. The checksum bits

are generated and written to the memory when the data bits are written, as shown in the following figure.

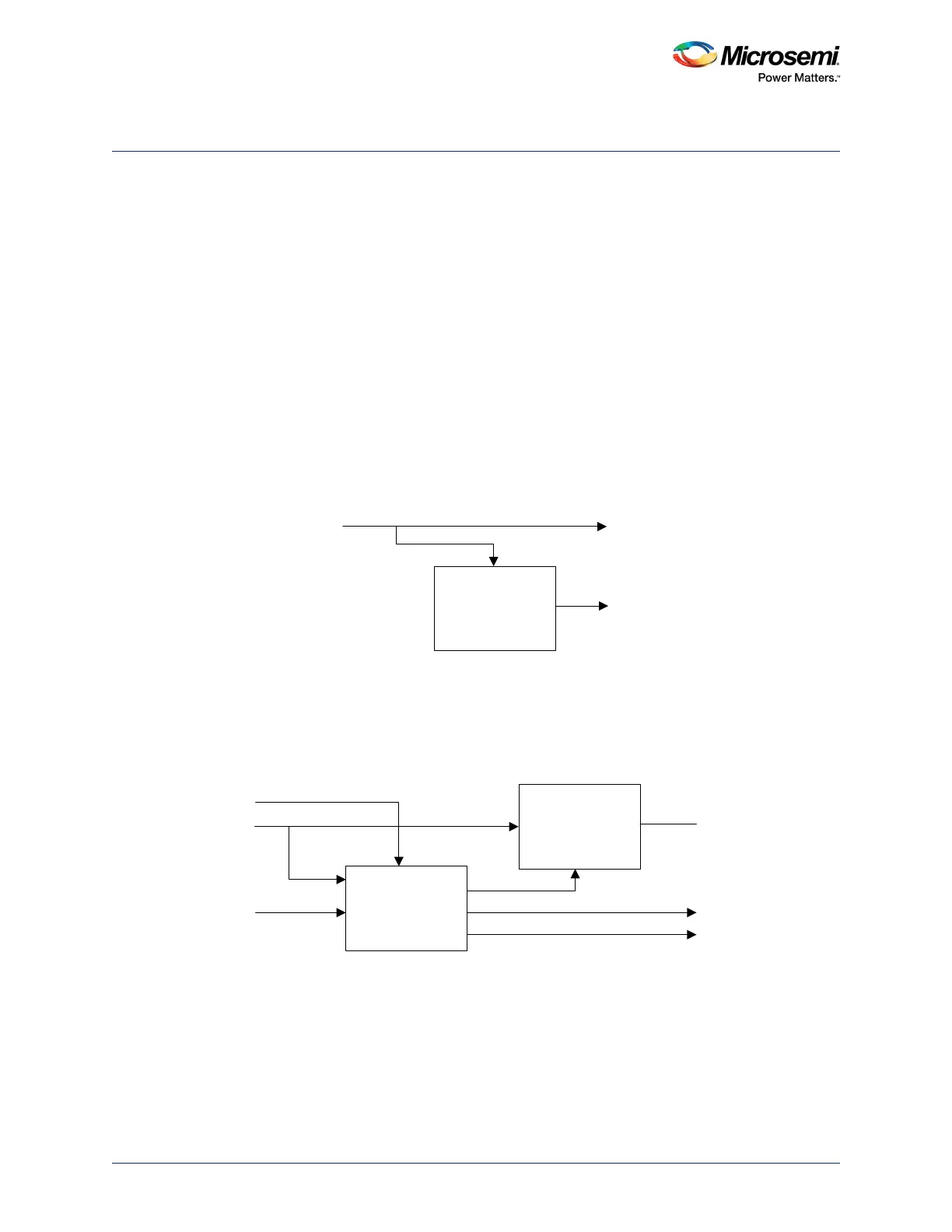

When the word is read, the checksum bits are utilized to determine whether one or more bits are in error.

If the error is a single-bit error, checksum bits determine which bit contains the error. EDAC algorithms

implemented in SmartFusion2 SOC devices are designed to detect all two-bit errors and correct all

single-bit errors within a single word.

Figure 365 • EDAC in Write Mode

When data is written to a storage element in memory through EDAC, checksum bits are generated based

on the input data pattern. The checksum bits, along with the input data, are stored in the target memory.

This permits the data to propagate to the data storage element unchanged while the appropriate

checksum bits are generated to be stored along with the data.

Figure 366 • EDAC in Read Mode (Reading From Memory)

For a read operation, the checksum bits are computed from the Data In inputs, and XORed with the

Checksum Bits In inputs to form the error syndrome. The error syndrome is internally generated and is

not user-accessible.

If all bits of the error syndrome are 0, then there is no error. If one or more syndrome bits are 1, then an

error is detected as indicated by the output Err_detect = 1. If the error is not correctable (2 or more bits

errored), then it is indicated by the output Err_multpl = 1. The error syndrome indicates which bit is in

6\QGURPH

*HQHUDWRU

'DWD2XW

&KHFNVXP

%LWV2XW

'DWD,Q

6\QGURPH

*HQHUDWRU

'DWD2XW

'DWD,Q

&RUUHFW

&KHFNVXP

%LWV,Q

'DWD%LW

&RUUHFWLRQ

(UUBGHWHFW

(UUBPXOWSO

Loading...

Loading...