High Performance DMA Controller

UG0331 User Guide Revision 15.0 251

8.4.1.2 Descriptor 0 Source Address Register

8.4.1.3 Descriptor 1 Source Address Register

8.4.1.4 Descriptor 2 Source Address Register

8.4.1.5 Descriptor 3 Source Address Register

8.4.1.5.1 Notes on the Source Address Register (SAR)

• Address is word aligned at the start.

• Address increments on each successful transfer at the source end.

• HPDMA controller starts reading the data from source memory and transfers to destination memory.

• Software can write all 32-bit source address to prevent non-word aligned transfers at the start and 2

LSBs, 1:0, are masked in the hardware.

• The source address is updated when descriptor transfer is in progress.

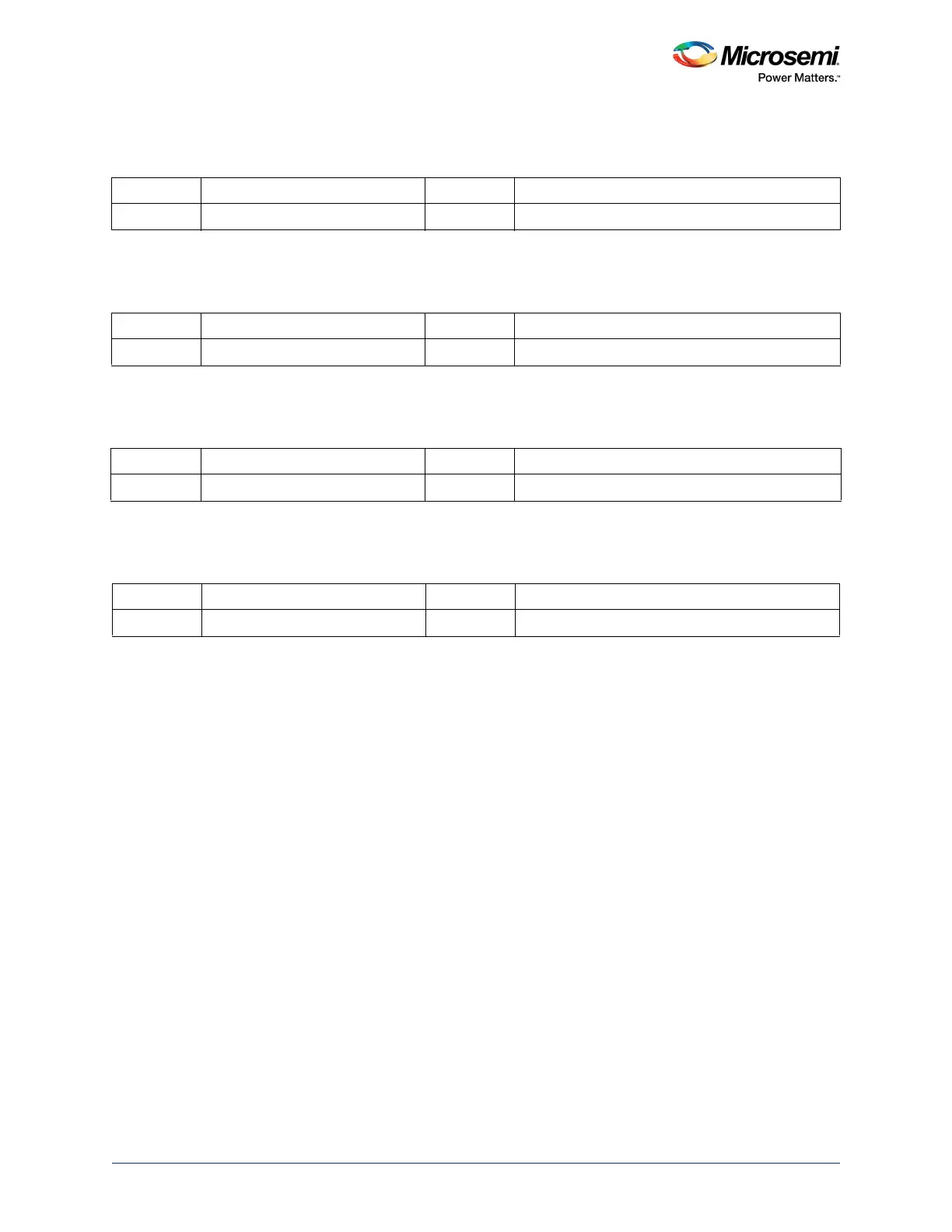

Table 151 • HPDMAD0SAR_REG

Bit Number Name Reset Value Description

31:0 HPDMASAR_DCP0_SRC_ADRS 0x00 Descriptor 0 source end memory start address

Table 152 • HPDMAD1SAR_REG

Bit Number Name Reset Value Description

31:0 HPDMASAR_DCP1_SRC_ADRS 0x00 Descriptor 1 source end memory start address

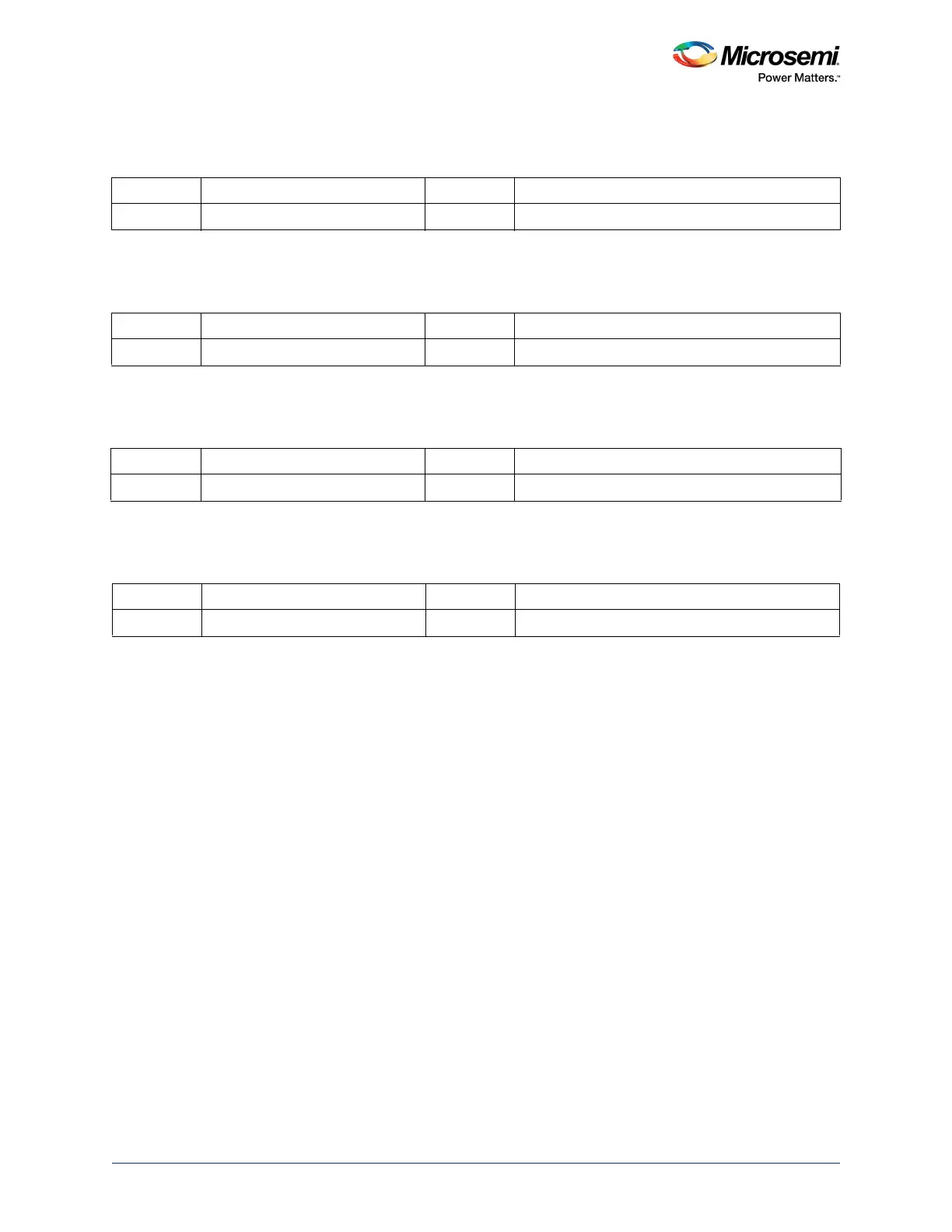

Table 153 • HPDMAD2SAR_REG

Bit Number Name Reset Value Description

31:0 HPDMASAR_DCP2_SRC_ADRS 0x00 Descriptor 2 source end memory start address

Table 154 • HPDMAD3SAR_REG

Bit Number Name Reset Value Description

31:0 HPDMASAR_DCP3_SRC_ADRS 0x00 Descriptor 3 source end memory start address

Loading...

Loading...