System Register Block

UG0331 User Guide Revision 15.0 698

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

22.3.27 USB I/O Input Select Control Register

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

22.3.28 Peripheral Clock MUX Select Control Register

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

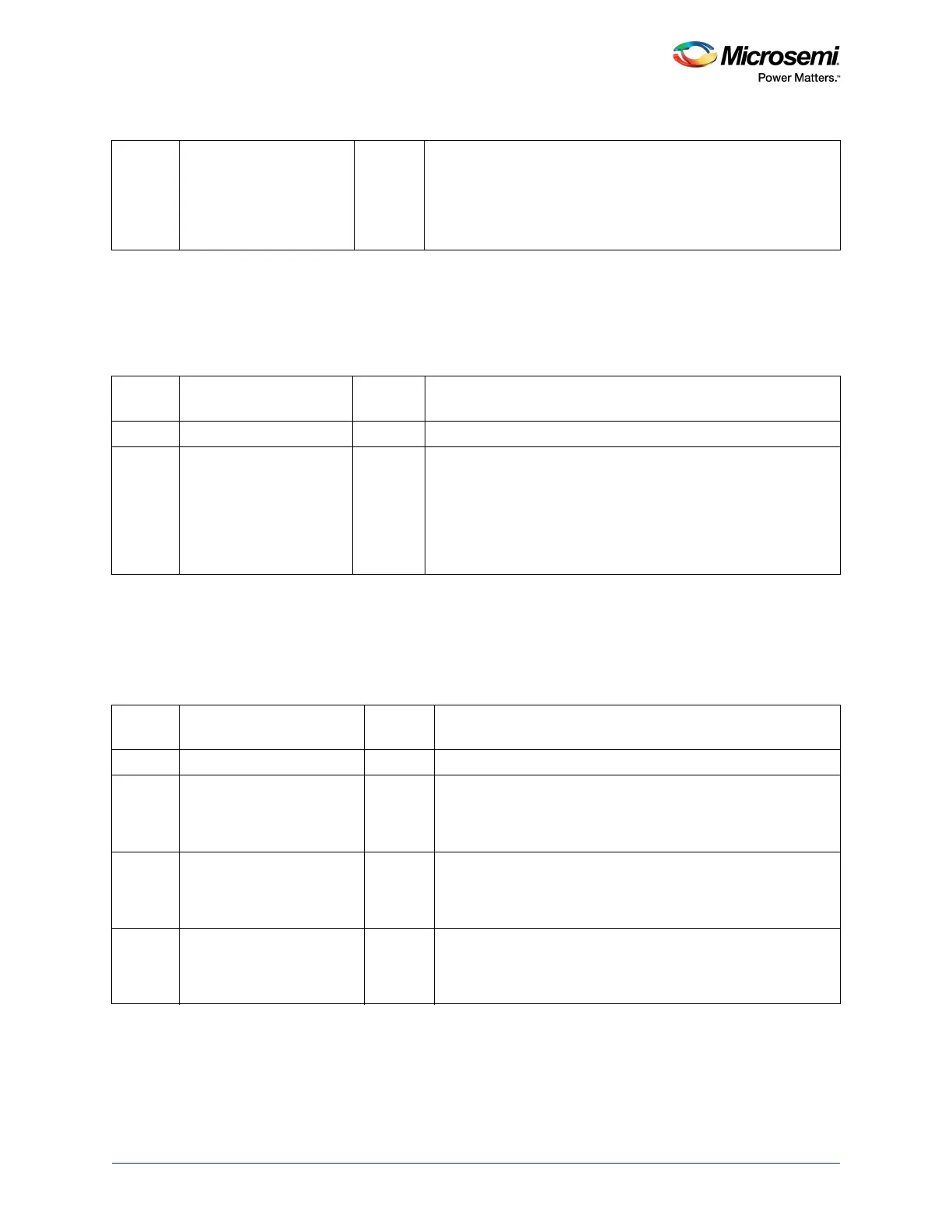

0 MDDR_CONFIG_LOCAL 0x1 Configures whether the MSS AHBTOAPB2 bridge can directly

access the APB slave within the MDDR subsystem or whether the

APB slave is connected to the fabric. Allowed values:

0: AHBTOAPB2 bridge cannot access MDDR APB slave

1: AHBTOAPB2 bridge can access MDDR APB slave

Reset signal for this bit is CC_RESET_N.

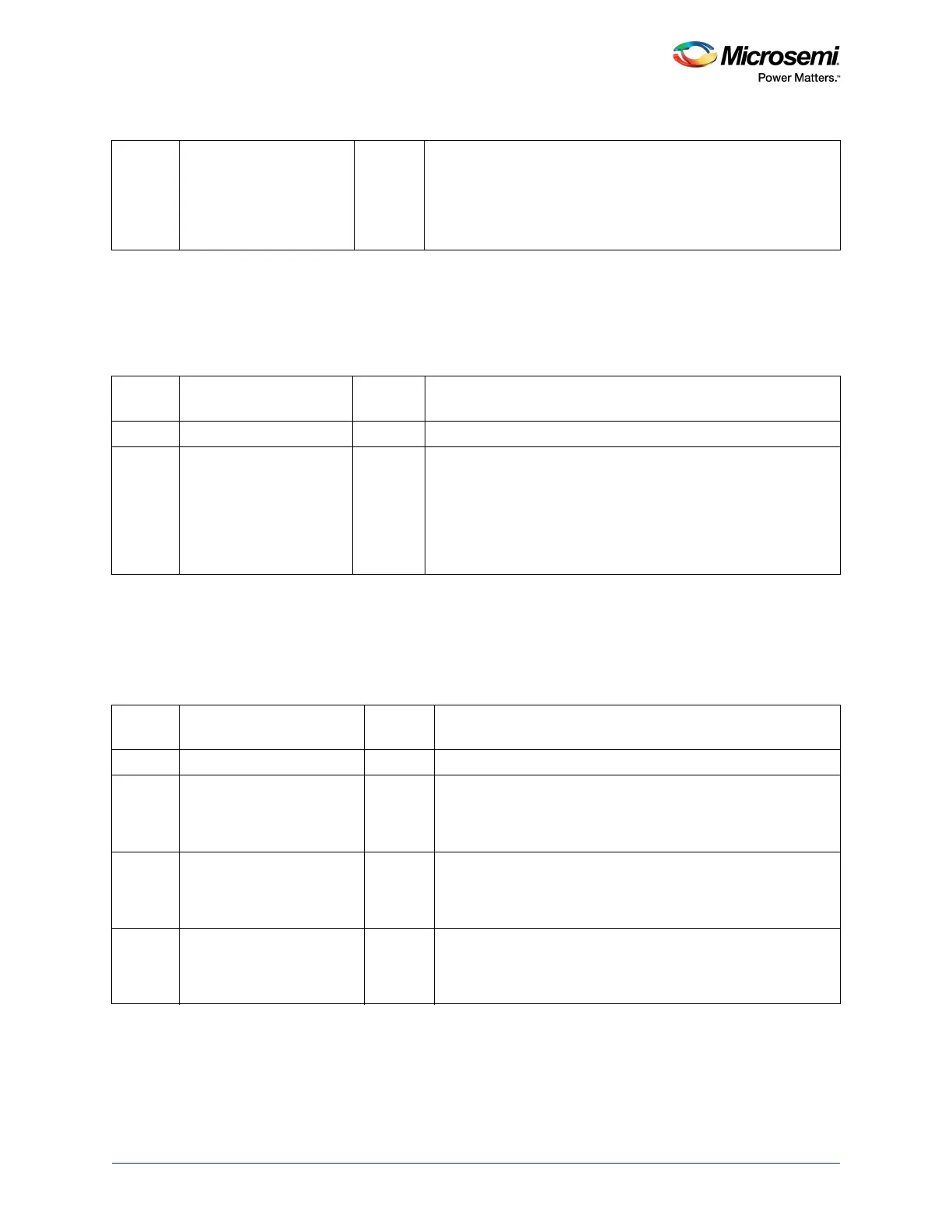

Table 681 • USB_IO_INPUT_SEL_CR

Bit

Number Name

Reset

Value Description

[31:2] Reserved 0

[1:0] USB_IO_INPUT_SEL 0 Selects one of the four USB data interfaces from IOMUXCELLs

and I/O pads. Depending on the device and package, not all

interfaces may be available. Allowed values:

00: USBA interface can be connected to USB

01: USBB interface can be connected to USB

10: USBC interface can be connected to USB

11: USBD interface can be connected to USB

Table 682 • PERIPH_CLK_MUX_SEL_CR

Bit

Number Name

Reset

Value Description

[31:3] Reserved 0

2 TRACECLK_DIV2_SEL 0 Selects whether the Cortex-M3 processor trace clock source is

M3_CLK or M3_CLK/2. Allowed values:

0: M3_CLK selected as source of TRACECLKIN_I

1: M3_CLK/2 selected as source of TRACECLKIN_I

1 SPI1_SCK_FAB_SEL 0 Selects the SPI1_SCK from the fabric or I/O pads. Allowed

values:

0: SPI1_SCK clock from I/O pads is selected and fed to SPI1

1: SPI1_SCK clock from the fabric is selected and fed to SPI1

0 SPI0_SCK_FAB_SEL 0 Selects the SPI0_SCK from the fabric or I/O pads. Allowed

values:

0: SPI0_SCK clock from I/O pads is selected and fed to SPI0

1: SPI0_SCK clock from fabric is selected and fed to SPI0

Table 680 • MDDR_CR (continued)

Loading...

Loading...