Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 368

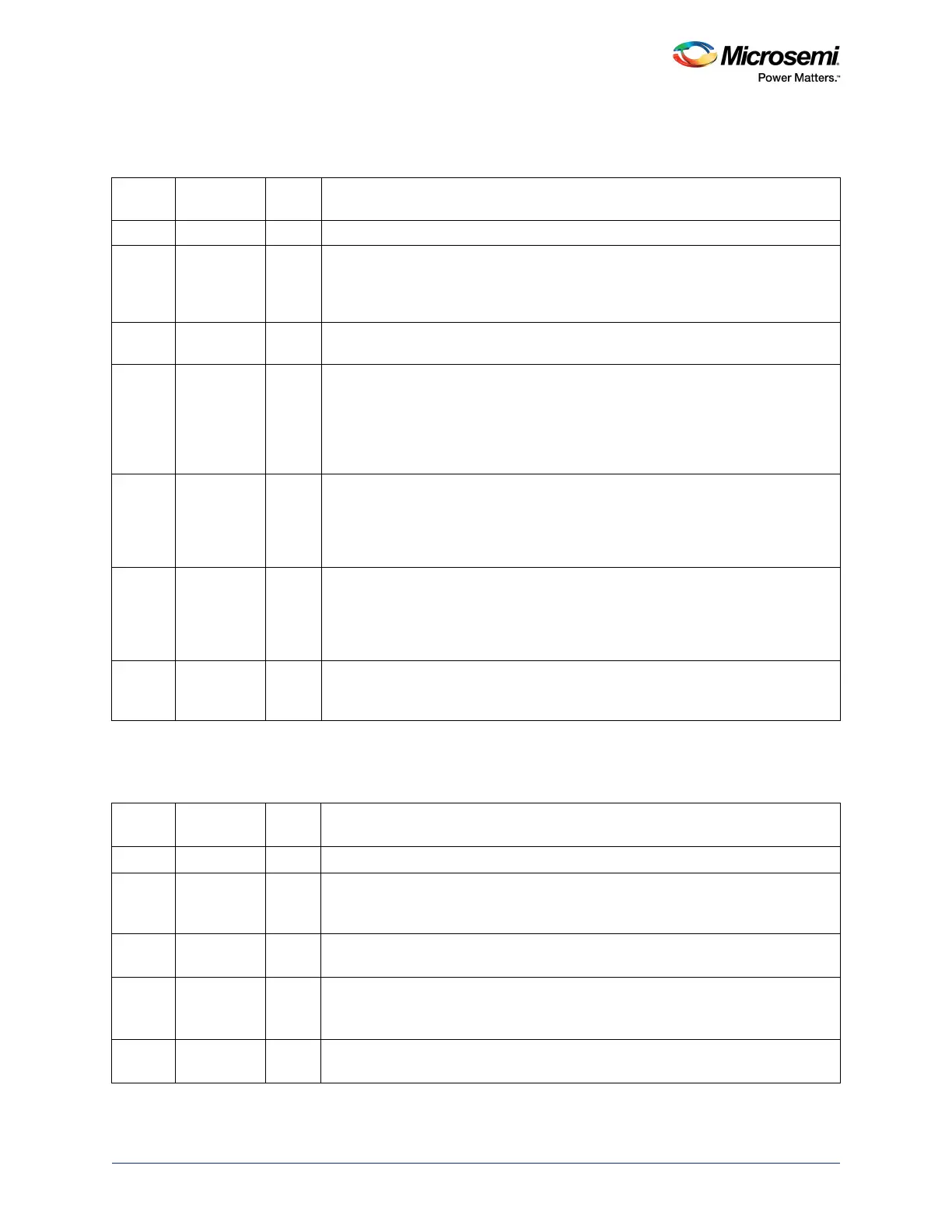

10.3.14.6 LPM_INTR_REG (Peripheral) Bit Definitions

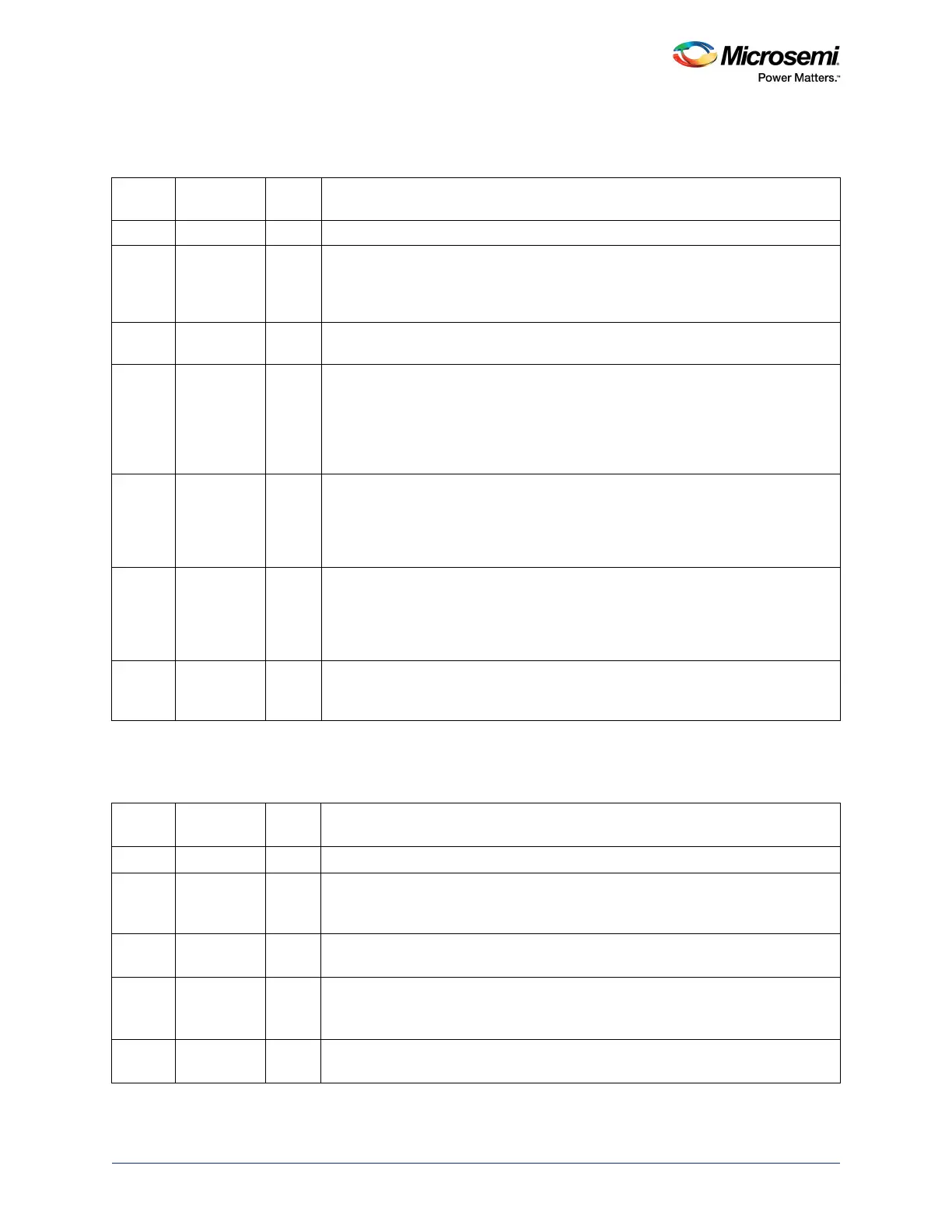

10.3.14.7 LPM_INTR_REG (Host) Bit Definitions

Table 309 • LPM_INTR_REG (0x40043364)(Peripheral Mode)

Bit

Number Name

Reset

Value Function

[7:6] Reserved N/A

5 LPMERR 0 This bit is set if an LPM transaction is received that has a LinkState field

(LINK_ATTR_REG.bits[3:0]) that is not supported. In this case, the response to the

transaction is a STALL. However, the LINK_ATTR_REG is updated so that software

can observe the noncompliant LPM packet payload.

4 LPMRES 0 This bit is set when the USB controller has been resumed for any reason. This bit is

mutually exclusive from RESUME (POWER_REG.bit2).

3 LPMNC 0 This bit is set when an LPM transaction is received and the USB controller

responds with a NYET due to data pending in the received FIFOs. This can only

occur under the following condition:

The LPMEN field (LPM_CTRL_REG.bit[3:2]) is set to 11, the LPMXMT

(LPM_CTRL_REG.bit0) is set to 1, and there is data pending in the USB controller

transmit FIFOs.

2 LPMACK 0 This bit is set when an LPM transaction is received and the USB controller

responds with an ACK. This can only occur under the following condition:

The LPMEN field (LPM_CTRL_REG.bit[3:2]) is set to 11, the LPMXMT

(LPM_CTRL_REG.bit0) is set to 1, and there is data pending in the USB controller

transmit FIFOs.

1 LPMNY 0 This bit is set when an LPM transaction is received and the USB controller

responds with a NYET. This can only occur under the following conditions:

The LPMEN field (LPM_CTRL_REG.bit[3:2]) is set to 11, the LPMXMT

(LPM_CTRL_REG.bit0) is set to 1, and there is data pending in the USB controller

transmit FIFOs.

0 LPMST 0 This bit is set when an LPM transaction is received and the USB controller

responds with a STALL. This can only occur under the following condition:

The LPMEN field (LPM_CTRL_REG.bit[3:2]) is set to 01.

Table 310 • LPM_INTR_REG (0x40043364) (Host Mode)

Bit

Number Name

Reset

Value Function

[7:6] Reserved N/A

5 LPMERR 0 This bit is set if a response to the LPM transaction is received with a bit stuff error or

a PID error. In this case, suspend does not occur and the state of the device is

unknown.

4 LPMRES 0 This bit is set when the USB controller has been resumed for any reason. This bit is

mutually exclusive from RESUME (POWER_REG.bit2).

3 LPMNC 0 This bit is set when an LPM transaction has been transmitted and has failed to

complete. The transaction would have failed either because a timeout is occurred

or there are bit errors in the response for three attempts.

2 LPMACK 0 This bit is set when an LPM transaction is transmitted and the device responds with

an ACK.

Loading...

Loading...