Fabric Interface Interrupt Controller

UG0331 User Guide Revision 15.0 756

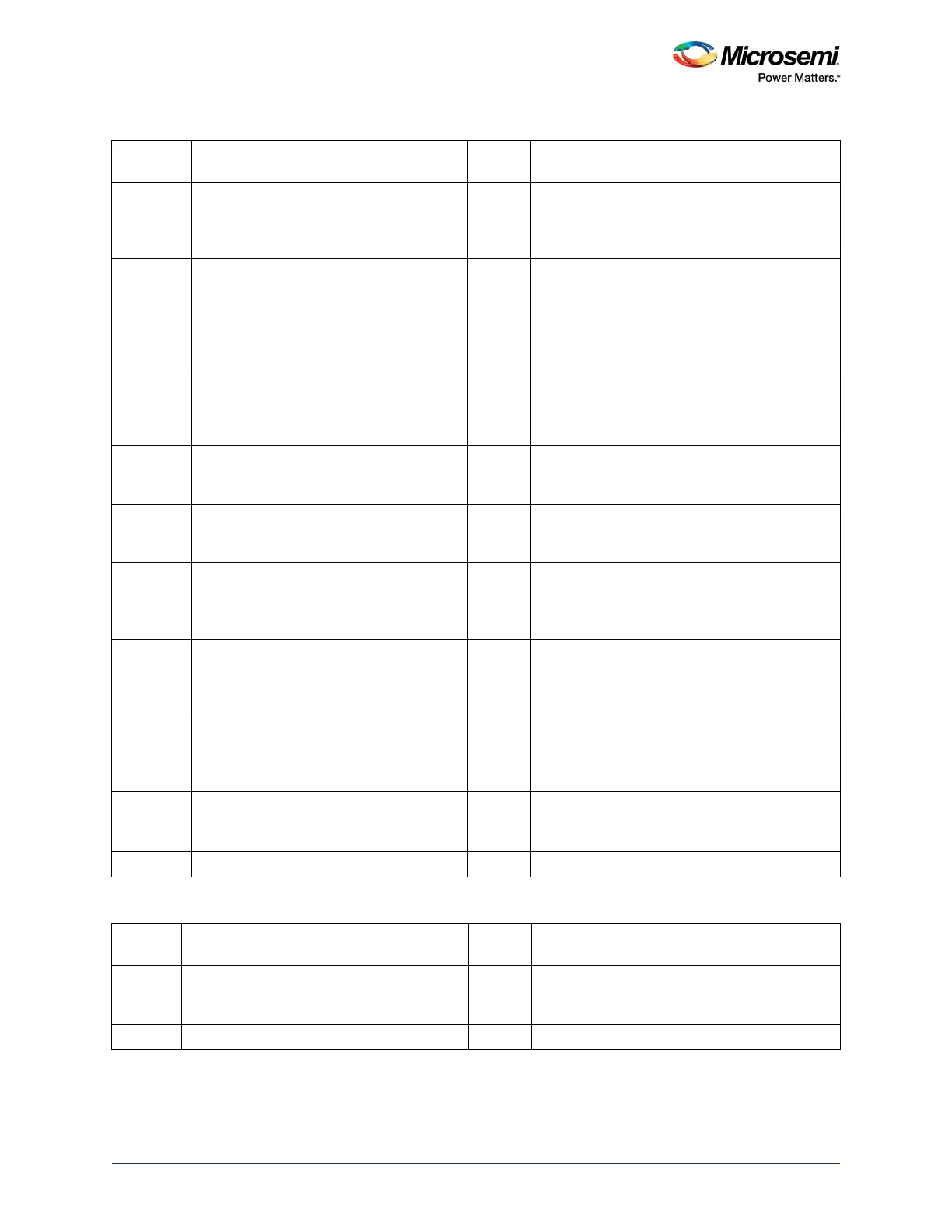

22 HPD_XFR_ERR_INT_STATUS 0 Set if the interrupt source for

HPD_XFR_ERR_INT is asserted and the

HPD_XFR_ERR_INT_ENBL interrupt enable bit

in INTERRUPT_ENABLE0 is High.

23 MSSDDR_PLL_LOCK_INT_STATUS 0 Set if the interrupt source for

MSSDDR_PLL_LOCK_INT is asserted and the

MSSDDR_PLL_LOCK_INT_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

MSSDDR_PLL_LOCK_INT interrupt is asserted

when MPLL achieves lock.

24 SW_ERRORINTERRUPT_STATUS 0 Set if the interrupt source for

SW_ERRORINTERRUPT is asserted and the

SW_ERRORINTERRUPT_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

25 DDRB_INTR_STATUS 0 Set if the interrupt source for DDRB_INTR is

asserted and the DDRB_INTR_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

26 ECCINTR_STATUS 0 Set if the interrupt source for ECCINTR is

asserted and the ECCINTR_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

27 CACHE_ERRINTR_STATUS 0 Set if the interrupt source for CACHE_ERRINTR

is asserted and the CACHE_ERRINTR_ENBL

interrupt enable bit in INTERRUPT_ENABLE0 is

High.

28 SOFTINTERRUPT_STATUS 0 Set if the interrupt source for SOFTINTERRUPT

is asserted and the SOFTINTERRUPT_ENBL

interrupt enable bit inINTERRUPT_ENABLE0 is

High.

29 COMBLK_INTR_STATUS 0 Set if the interrupt source for COMBLK_INTR is

asserted and the COMBLK_INTR_ENBL

interrupt enable bit in INTERRUPT_ENABLE0 is

High.

30 USB_DMA_INT_STATUS 0 Set if the interrupt source for USB_DMA_INT is

asserted and USB_DMA_INT_ENBL interrupt

enable bit in INTERRUPT_ENABLE0 is High.

31 Reserved 0 Reserved

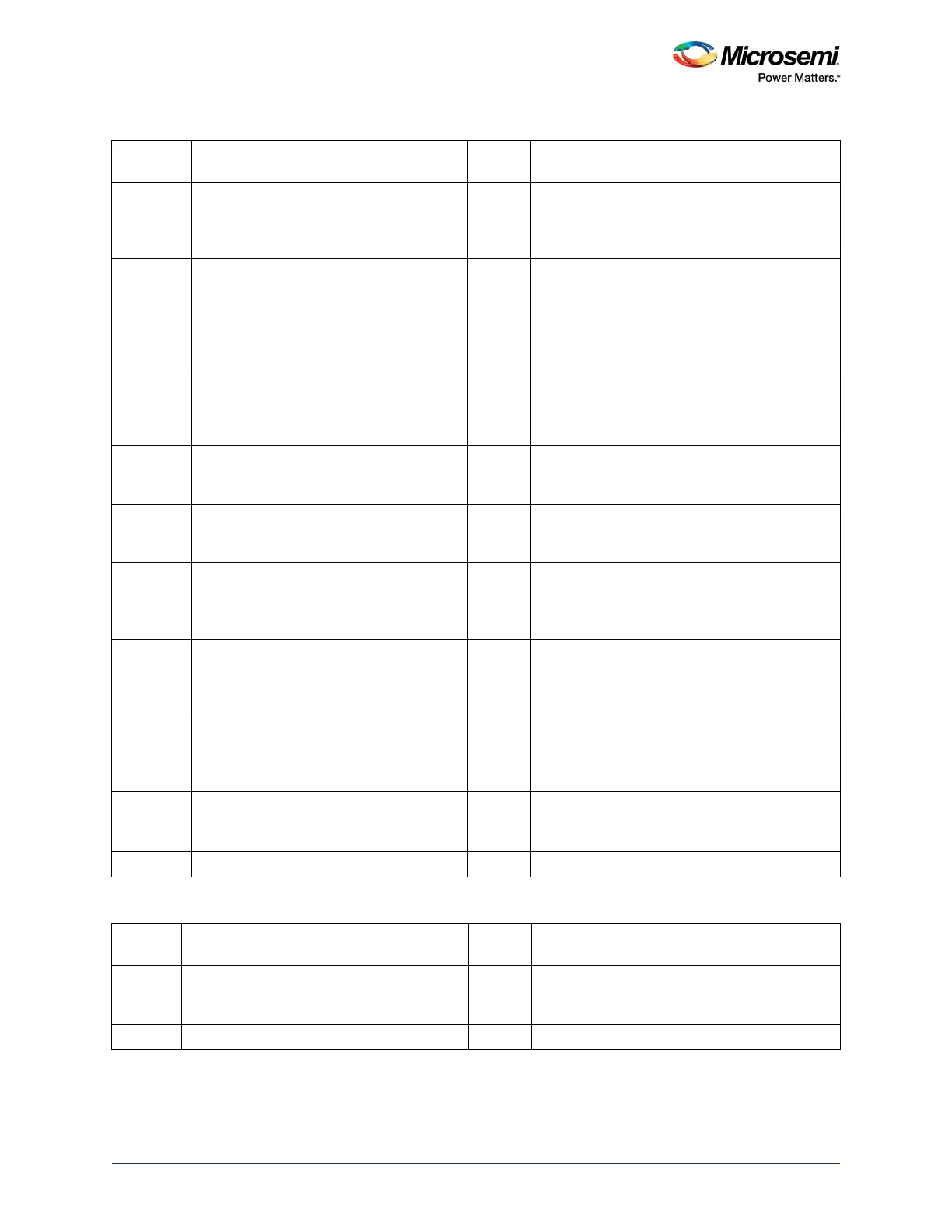

Table 776 • INTERRUPT_MODE

Bit

Number Name

Reset

Value Description

0 SELECT_MODE 0 The following are the valid values for this bit:

0: Select group 0

1: Select group 1

31:1 Reserved 0 Reserved

Table 775 • INTERRUPT_REASON0 (continued)

Bit

Number

Name

Reset

Value

Description

Loading...

Loading...