MMUART Peripherals

UG0331 User Guide Revision 15.0 500

13.4.13 Scratch Register (SR)

13.4.14 Multi-Mode Control Register 0 (MM0)

1 DDSR R 0 Delta data set ready (DDSR) indicator. Indicates that the DSRn input has

changed state since the last time it was read by the Cortex-M3 processor.

Whenever bit 0, 1, 2, or 3 is set to 1, a modem status interrupt is

generated.

0 DCTS R 0 Delta clear to send (DCTS) indicator. Indicates that the CTSn input has

changed state since the last time it was read by the Cortex-M3 processor.

Whenever bit 0, 1, 2, or 3 is set to 1, a modem status interrupt is

generated.

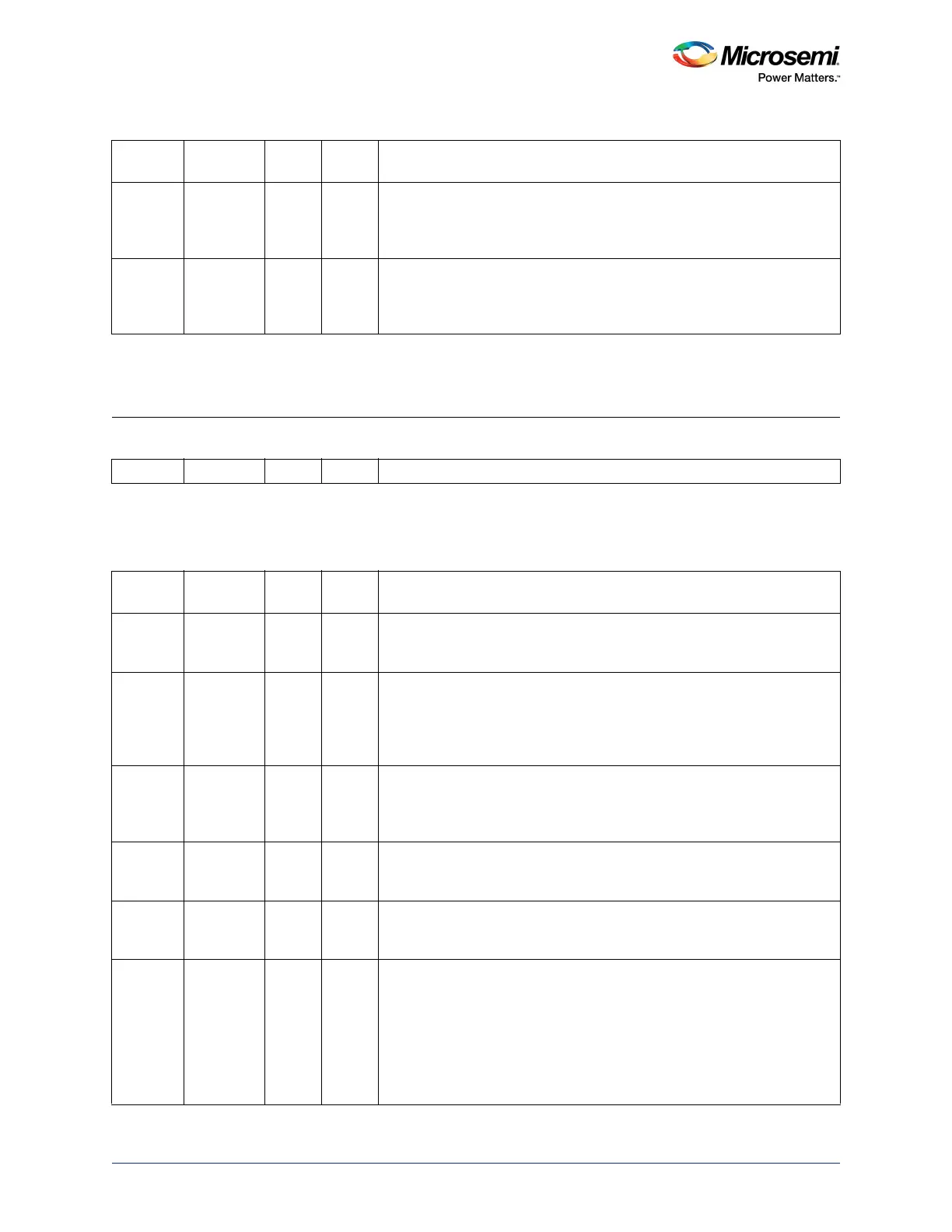

Table 484 • SR

Bit

Number Name R/W

Reset

Value Description

[7:0] SCR R/W 0 Scratch register. This register has no effect on MMUART_x operation.

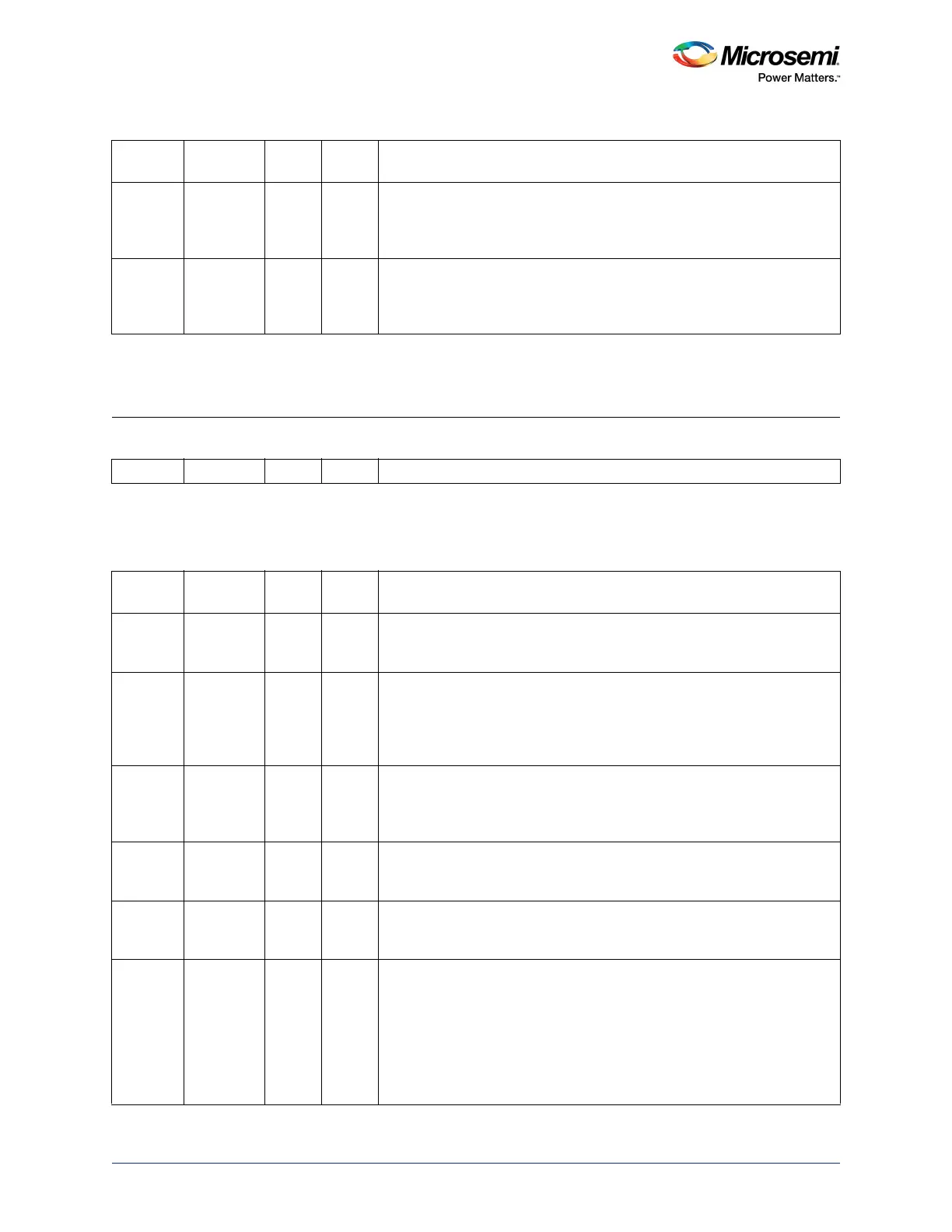

Table 485 • MM0

Bit

Number Name R/W

Default

State Description

7 EFBR R/W 0 Enable fractional baud rate (FBR) mode.

0: Disabled (default)

1: Enabled

6 ERTO R/W 0 Enable receiver timeout (RTO). Writing this bit enables the timeout and

restarts the counter value. The timeout value is determined by the RTO

register.

0: Disabled (default)

1: Enabled

5 ETTG R/W 0 Enable transmitter time guard (TTG). The time guard value is determined

by the TTG Register.

0: Disabled (default)

1: Enabled

4 Reserved R/W 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read- modify-write operation

3 ELIN R/W 0 Enable LIN header detection and automatic baud rate calculation.

0: Disabled (default)

1: Enabled

[2:0] ESYN R/W 0 Enable synchronous operation. There are four types of Synchronous

Operation modes that can be enabled.

0b000: Disabled, that is, Asynchronous mode (default)

0b001: Synchronous slave enabled, positive-edge clock

0b010: Synchronous slave enabled, negative-edge clock

0b011: Synchronous master enabled, positive-edge clock

0b100: Synchronous master enabled, negative-edge clock

0b101, 0b110, and 0b111: Reserved

Table 483 • MSR (continued)

Bit

Number Name R/W

Reset

Value Description

Loading...

Loading...