Communication Block

UG0331 User Guide Revision 15.0 598

17.5 COMM_BLK Register Interface Details

This section describes the COMM_BLK registers in detail.

17.5.1 Control Register

17.5.2 Status Register

This register provides status information. R/W bits are cleared by writing 1. FIFO empty full flags will

automatically clear as FIFO is full and empty.

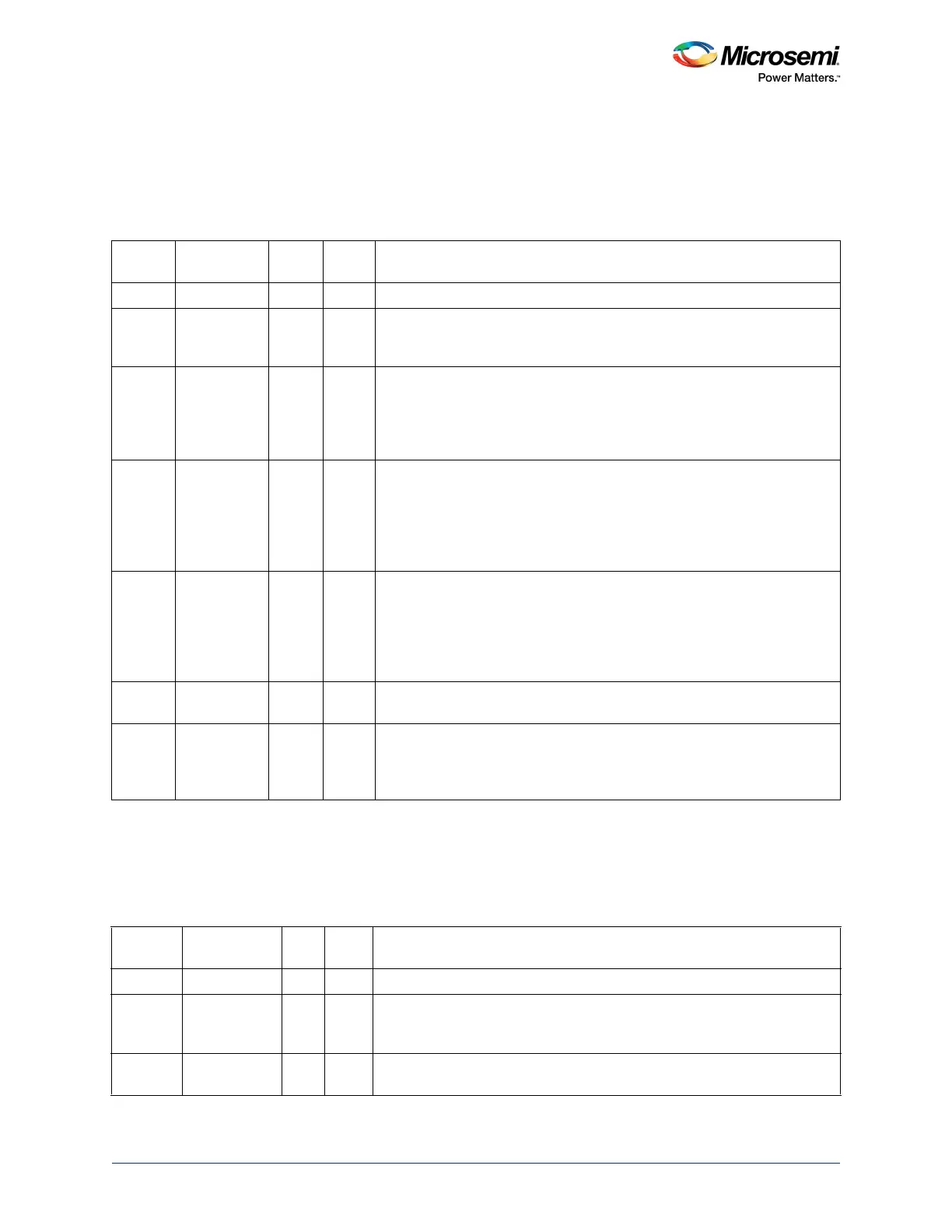

Table 594 • CONTROL

Bit

Number Name R/W

Reset

Value Description

[7:6] RESERVED R 00 Reserved

5 LOOPBACK R/W 1 After system reset the COMM_BLK is in Loopback mode. Set LOOPBACK

bit to ‘0’ to disable the loopback (Normal operation). It is used for factory

test.

4 ENABLE R/W 0 Configure the COMM_BLK interface.

0: Disables COMM_BLK

1: Enables COMM_BLK

Enable COMM_BLK before writing to the FIFO and leave it enabled if it is

being used.

3 SIZERX R/W 0 Sets the number of bytes that each APB transfer reads from the RX FIFO.

0: 1 Byte

1: 4 Bytes (32-bits)

This setting effects the behavior of the RxRDY signal and RCVOKAY flags.

When set to 0 the flags indicate that a byte can be read and when set to 1

it indicates that a word can be read.

2 SIZETX R/W 0 Sets the number of bytes that each APB transfer writes into the TX FIFO.

0: 1 Byte

1: 4 Bytes (32-bits)

This setting effects the behavior of TxRDY signal and TXTOKAY. When set

to 0 the flags indicate that a byte can be written and when set to 1 it

indicates that a word can read be written.

1 FLUSHIN R 0 Indicates FIFO flush status. 1 indicates flush process is in progress.

0 indicates that flush process is completed.

0 FLUSHOUT R/W 0 Flush all FIFO’s. Writing 1 to this bit starts the flush process. When the

flush process is complete this bit returns to 0 automatically. The flush

process takes several clock cycles to complete, depending on the various

clock rates. Writing 0 has no effect.

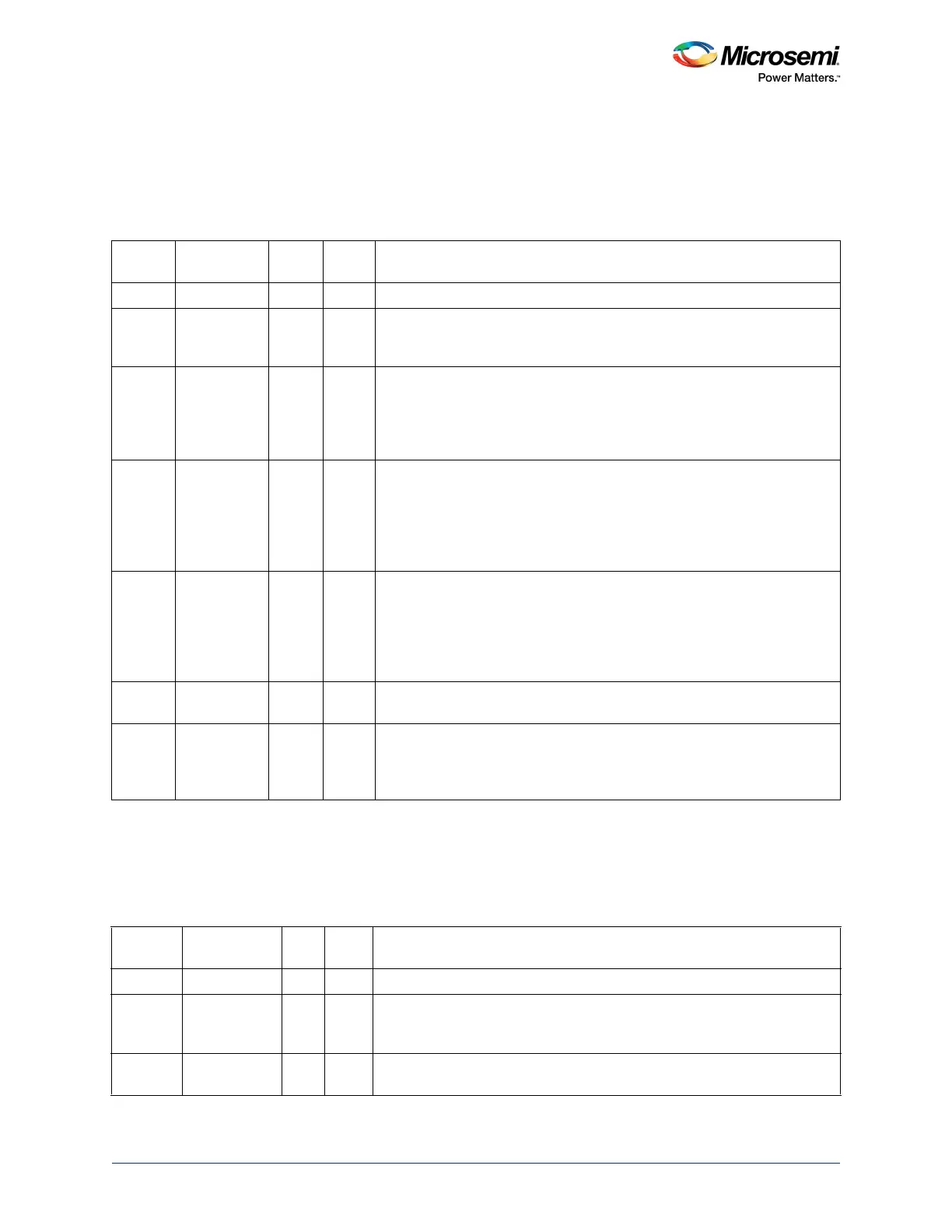

Table 595 • STATUS

Bit

Number Name R/W

Reset

Value Description

7 COMMAND R 0 First byte queued in receive FIFO has the command marker set

6 SIIERROR R/W 0 When an SII transfer (MSS to SII) is in progress, the start of frame marker

is set on one or more of the bytes.

Write 1 to clear

5 FLUSHRCVD R/W 0 Indicates that a FLUSH has been received.

Write 1 to clear

Loading...

Loading...