Ethernet MAC

UG0331 User Guide Revision 15.0 400

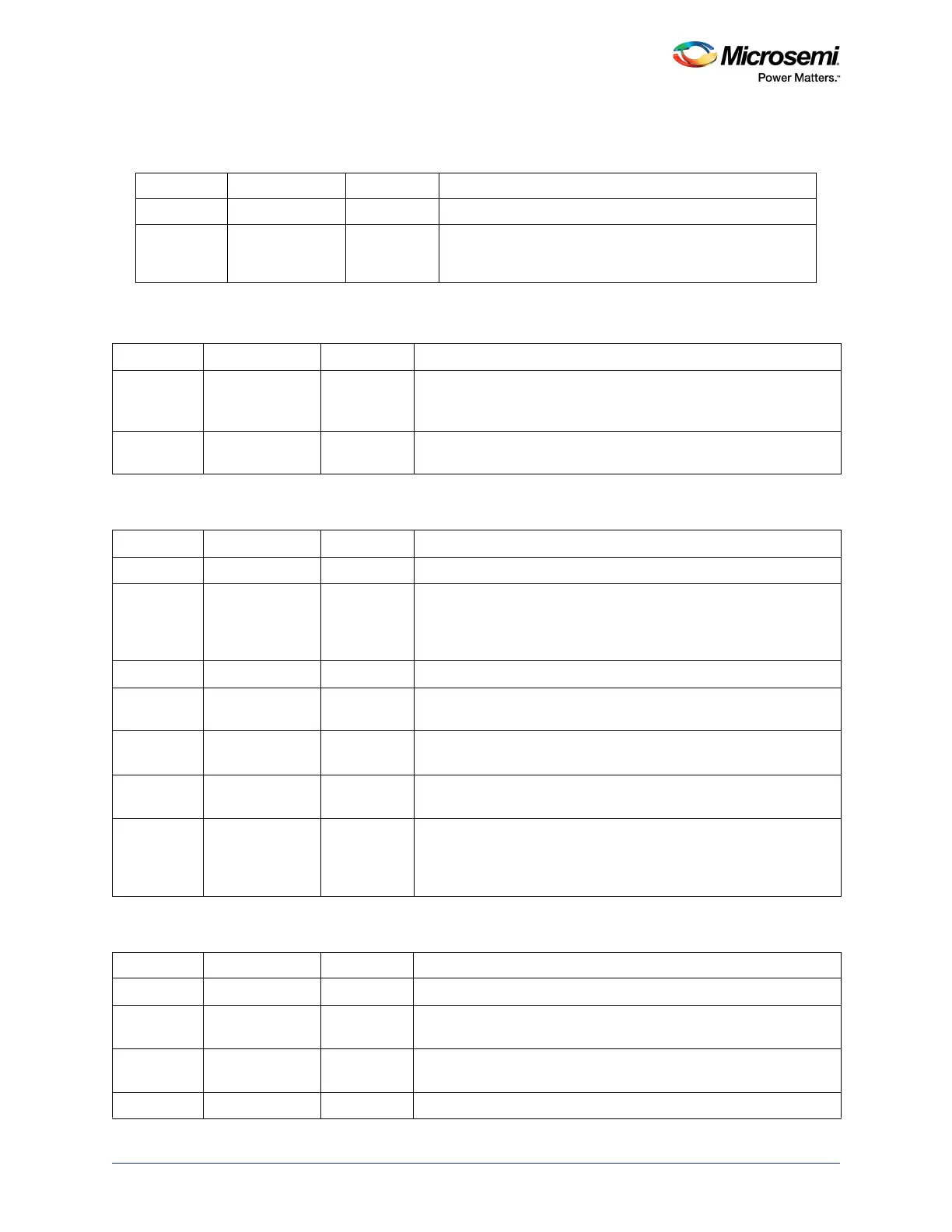

Table 342 • DMA_RX_CTRL

Bit Number Name Reset Value Description

[31:1] Reserved 0x0 Reserved

0 Rx Enable 0x0 Setting this bit enables DMA receive packet transfers.

The bit is cleared by the built-in DMA controller whenever it

encounters an Rx overflow or bus error state.

Table 343 • DMA_RX_DESC

Bit Number Name Reset Value Description

[31:1] Top 30 bits of

Descriptor

Address

0x0 When RxEnable is set by the host, the built-in DMA controller reads

this register to discover the location in the host memory of the first

receive packet descriptor.

0 Ignored by the

DMA controller

0x0 All descriptors are 32-bit aligned in the host memory.

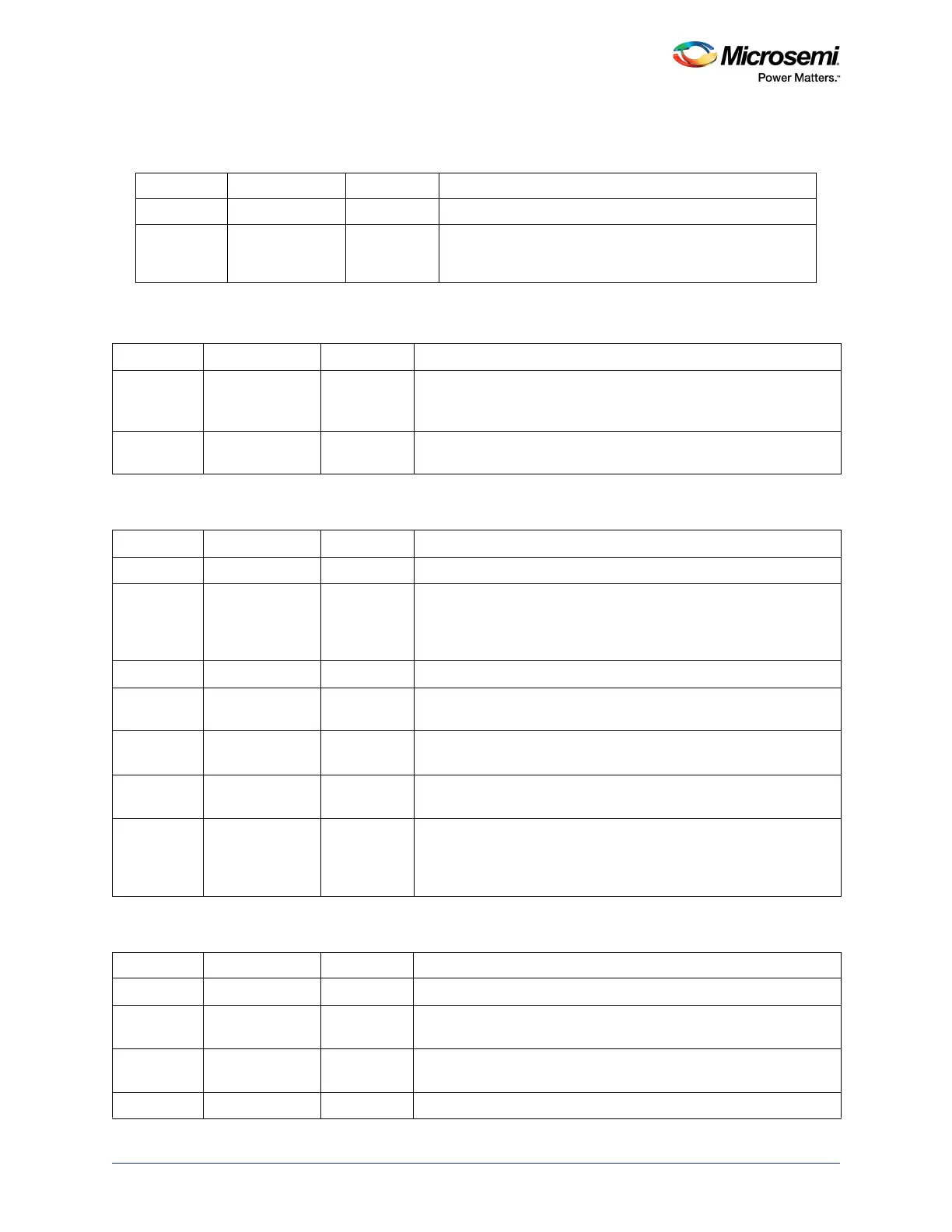

Table 344 • DMA_RX_STATUS

Bit Number Name Reset Value Description

[31:24] Reserved 0x0 Reserved

[23:16] RxPktCount 0x0 The 8-bit receive packet counter that is incremented whenever the

built-in DMA controller successfully transfers a packet, and is

decremented whenever the host writes a ‘1’ to bit zero of this

register.

[16:4] Reserved 0x0 Reserved

3 BusError 0x0 When set, this indicates that a host slave split, retry or error

response is received by the DMA controller.

2 RxOverflow 0x0 Set whenever the DMA controller reads a zero empty flag in the

descriptor it is processing.

1 Reserved 0x0 Reserved

0 RxPktReceived 0x0 When set, this indicates that one or more packets have been

successfully transferred. Writing a ‘1’ to this bit reduces the

RxPktCount value by one. The bit is cleared whenever RxPktCount

is zero.

Table 345 • DMA_IRQ_MASK

Bit Number Name Reset Value Description

[31:8] Reserved 0x0 Reserved

7 Bus Error Mask 0x0 Setting this bit to ‘1’ enables the Bus Error bit in the DMARxStatus

register as an interrupt source.

6 Rx Overflow

Mask

0x0 Setting this bit to ‘1’ enables the RxOverflow bit in the DMARxStatus

register as an interrupt source.

5 Reserved 0x0 Reserved

Loading...

Loading...