System Register Block

UG0331 User Guide Revision 15.0 733

22.3.100 Watchdog Timeout Event

22.3.101 Clear MSS Counters

22.3.102 Clear EDAC Counters

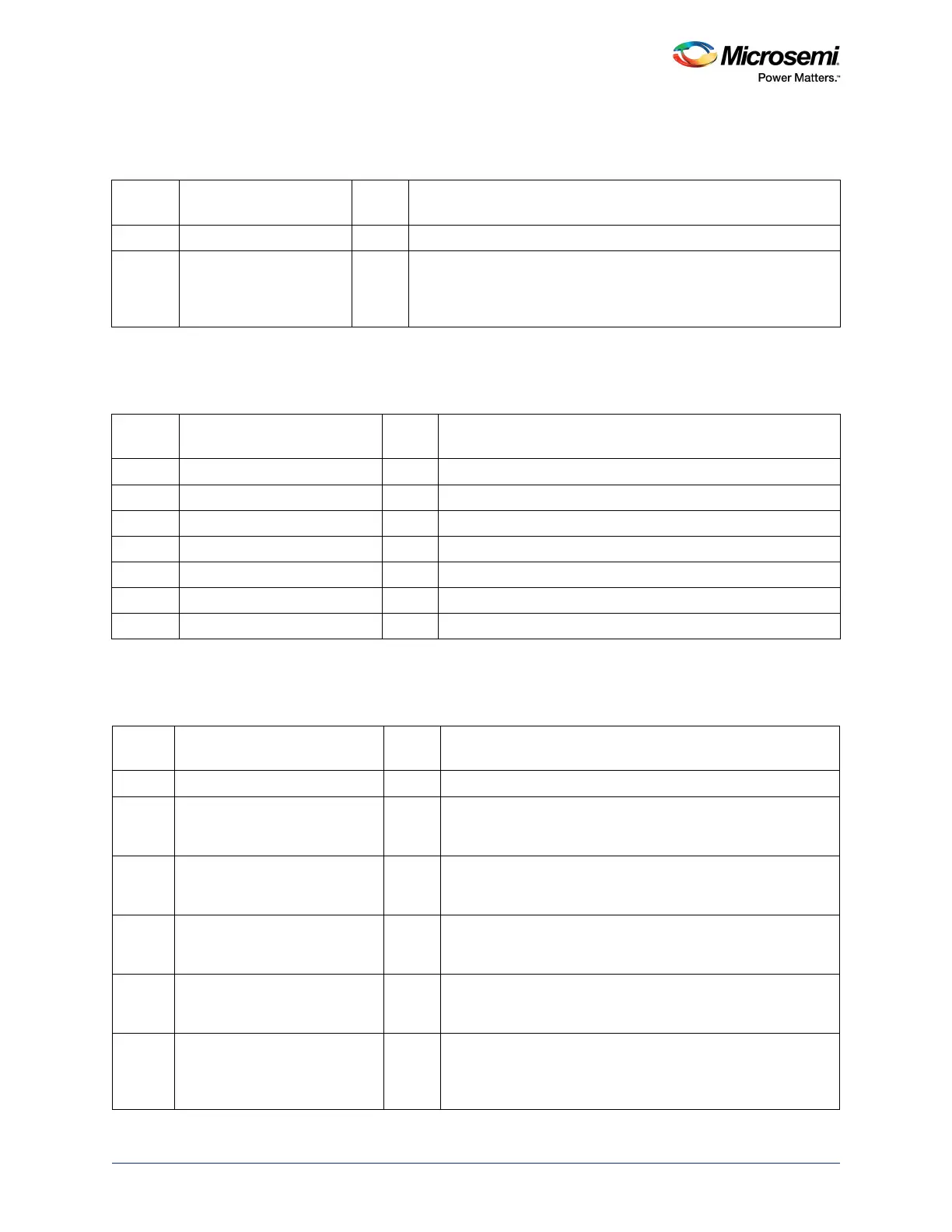

Table 758 • WDOGTIMEOUTEVENT

Bit

Number Name

Reset

Value Description

[31:1] Reserved 0

0 WDOGTIMEOUTEVENT 0 WDOGTIMEOUTEVENT is not affected by SYSRESETN. This

allows firmware to determine if a system reset occurred due to a

watchdog timeout event. This signal is not used as an interrupt to the

Cortex-M3 processor. Reset to 0 by PORESETN only.

Table 759 • CLR_MSS_COUNTERS

Bit

Number Name

Reset

Value Description

[31:6] Reserved 0

5 CC_DC_TRANS_CNTCLR 0 When set, the CC_DC_TRANS_CNT counter is reset.

4 CC_IC_TRANS_CNTCLR 0 When set, the CC_IC_TRANS_CNT counter is reset.

3 CC_DC_HIT_CNTCLR 0 When set, the CC_DC_HIT_CNT counter is reset.

2 CC_DC_MISS_CNTCLR 0 When set, the CC_DC_MISS_CNT counter is reset.

1 CC_IC_HIT_CNTCLR 0 When set, the CC_IC_HIT_CNT counter is reset.

0 CC_IC_MISS_CNTCLR 0 When set, the CC_IC_MISS_CNT counter is reset.

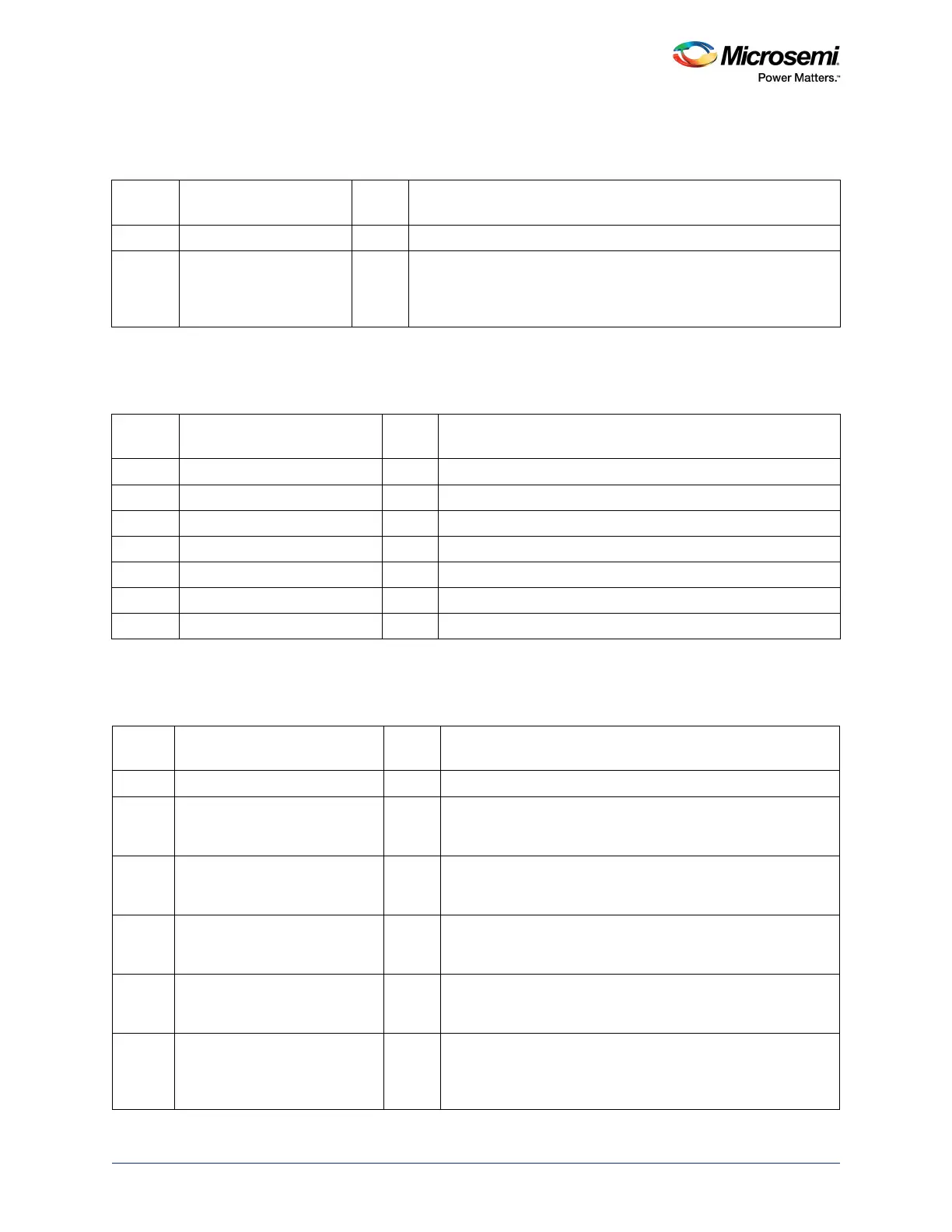

Table 760 • CLR_EDAC_COUNTERS

Bit

Number Name

Reset

Value Description

[31:14] Reserved 0

13 CAN_EDAC_CNTCLR_2E 0 Pulse generated to clear the 16-bit counter value in CAN

corresponding to the count value of EDAC 2-bit errors. This in

turn clears the upper 16 bits of the CAN_EDAC_CNT register.

12 CAN_EDAC_CNTCLR_1E 0 Pulse generated to clear the 16-bit counter value in CAN

corresponding to the count value of EDAC 1-bit errors. This in

turn clears the lower 16 bits of the CAN_EDAC_CNT register.

11 USB_EDAC_CNTCLR_2E 0 Pulse generated to clear the 16-bit counter value in USB

corresponding to the count value of EDAC 2-bit errors. This in

turn clears the upper 16 bits of the USB_EDAC_CNT register.

10 USB_EDAC_CNTCLR_1E 0 Pulse generated to clear the 16-bit counter value in USB

corresponding to the count value of EDAC 1-bit errors. This in

turn clears the lower 16 bits of the USB_EDAC_CNT register.

9 MAC_EDAC_RX_CNTCLR_2E 0 Pulse generated to clear the 16-bit counter value in Ethernet

MAC Rx RAM corresponding to the count value of EDAC 2-bit

errors. This in turn clears the upper 16 bits of the

MAC_EDAC_RX_CNT register.

Loading...

Loading...